51单片机片内有一个高增益的反相放大器,反相放大器的输入端为晶振引脚1,输出端为晶振引脚2。由该放大器构成的振荡电路和时钟电路一起构成了单片机的时钟方式。

根据硬件电路设计方案的不同,单片机的时钟连接方式可分为两种:内部时钟方式和外部时钟方式。

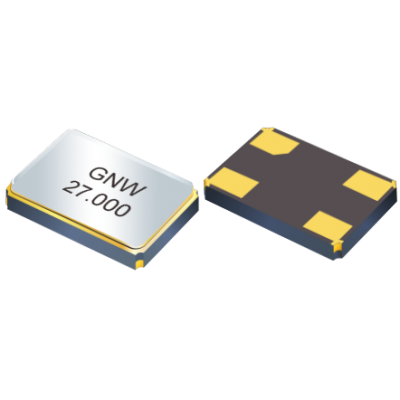

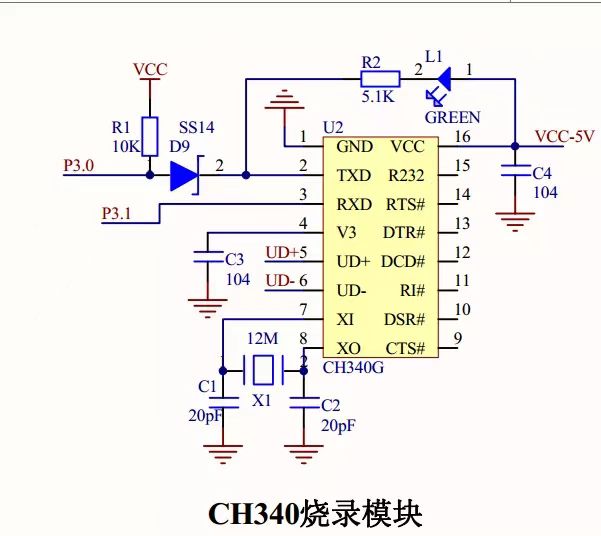

在内部方式时钟电路中,必须在晶振引脚1和晶振引脚2两端分别接两个外接电容构成振荡电路。如果测试晶振输出频率超出单片机捕捉范围,可以微调这两颗电容值的大小,是晶振频率尽可能靠近标称频率。若此方法失效,建议尝试选取更高精度的晶振。

通常来说,对于采用12MHz的方案,如果晶振的负载电容为20pF的话,两颗外接电容C1和C2取值为27pF至33pF比较合适。对于外接时钟电路,要求晶振引脚1接地,晶振引脚2接外部时钟。对于外部时钟信号的要求是确保脉冲宽度,时钟频率低于12MHz即可。

51单片机晶振电路基本原理:

晶振的振荡信号从晶振引脚2端送入内部时钟电路,该振荡信号被二分频,产生一个两相时钟信号P1和P2供单片机使用。时钟信号的周期称为状态时间S,它是振荡周期的2倍。P1信号在每个状态的前半周期有效,在每个状态的后半周期P2信号有效。CPU就是通过两相时钟P1和P2为基本节拍来协调单片机实现各部分的有效工作。

了解更多晶振相关资讯,请点击晶诺威官网以下链接:

- 如何减少辐射对时钟信号的干扰?

- 如何降低电磁对晶振时钟信号的干扰

- 晶振频率受干扰的不良现象和解决方案

- PCB晶振布线抗干扰(EMI)设计介绍

- 为何说提供时钟信号的晶振是数字电路的心脏?

- PCB设计中晶振时钟信号电路介绍

- 晶振PCB正确布线需要哪些注意事项?

- 从软件角度看晶振的作用及MCU工作流程

- EMC测试项目及电磁波对晶振的影响

- 晶振位于线路板边缘会带来哪些隐患?

- 晶振受电磁干扰的解决方案

- 晶振到芯片的距离为何越近越好?

- 如何选择高品质晶振生产厂家?

- 晶振振荡电路中负性阻抗到底是什么?

- 你对晶振的激励功率了解有多少?

- 晶振的激励功率怎么设定

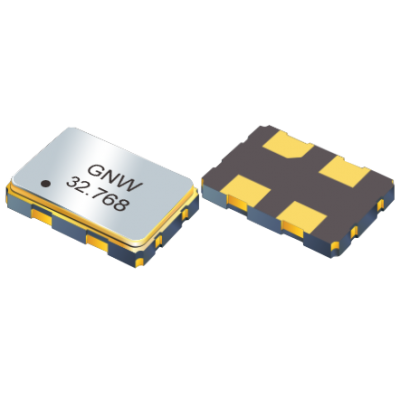

- 有源晶振的输出波形分类和应用介绍

- 晶振输出波形和电路形式介绍