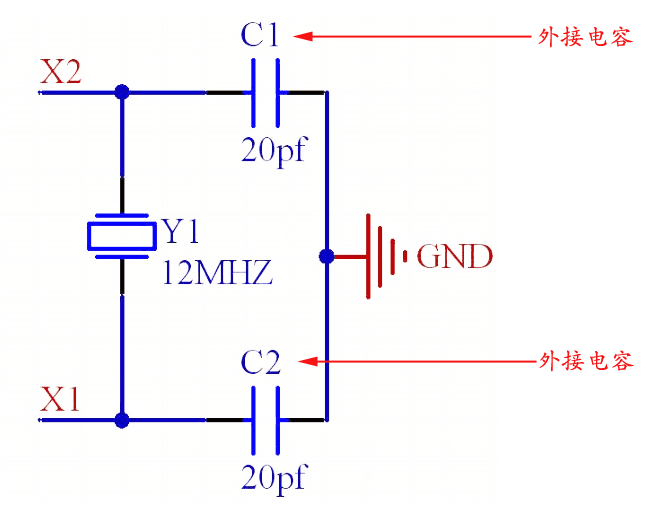

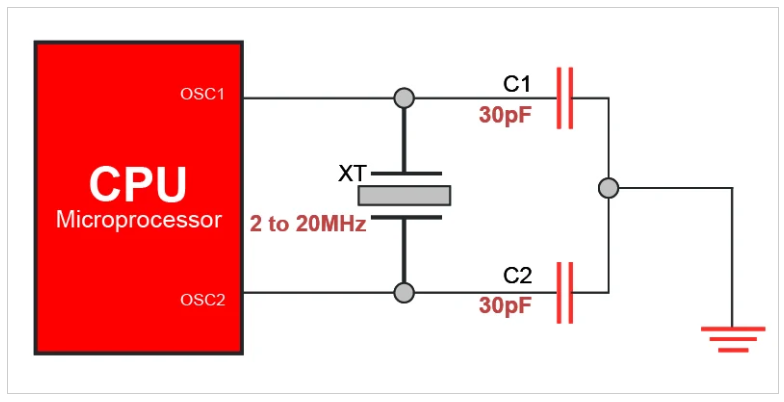

在使用外部晶振作为芯片的时钟信号源时,晶振的两个引脚需要分别串联两颗与之匹配的电容。千万不要小窥这两颗电容,如果没有它们,一般情况下晶振就无法正常工作。原理如下:

芯片晶振引脚的内部通常是一个反相器,芯片晶振的两个引脚之间还需要连接一个电阻,使反相器在振荡初始时处与线性状态,但这个电阻一般集成在芯片的内部,反相器就好像一个有很大增益的放大器,为了方便起振,晶振连接在芯片晶振引脚的输入和输出之间,等效为一个并联谐振回路, 振荡的频率就是石英晶振的并联谐振频率。

晶振旁边的两个电容需要接地,其实就是电容三点式电路的分压电容,接地点就是分压点,以分压点为参考点,振荡引脚的输入和输出是反相的,但从晶振两端来看,形成一个正反馈来保证电路能够持续振荡。

芯片设计的时候,其实这两个电容就已经形成,一般是容量相等,但容量比较小,不一定适合很宽的振荡频率范围,所以需要外接两颗负载电容。C1和C2是电路板和包括IC 和晶振在内的组件的总电容值。

晶振和外接电容布线注意事项:

为了让晶振能够可靠、稳定的起振,在布线设计时,需要考虑让晶振和外接电容尽量靠近芯片。

拓展阅读:增加两颗外接电容的作用

1、增加频率稳定

在不同的工作条件下,如电源电压波动或者温度变化,增加两颗电容可以提供更好的谐振频率。

2、补偿频率公差

无源晶振的标称负载电容,通常是一个范围,并非固定值,增加两颗电容可以灵活的调整实际的负载电容,适当补偿频率公差。

3、灵活设计电路

增加两颗电容使电路设计更灵活,工程师可根据实际应用需求来调整谐振回路的特性。

了解更多关于晶振电容匹配知识,请点击本网站以下链接: