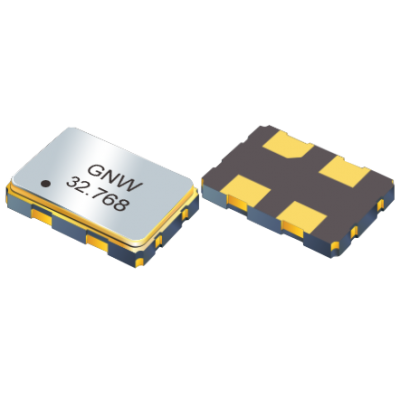

晶振的选择和PCB板布局的方式会对电路板功能及性能产生一定的影响。选择晶振时,除了频率、封装、精度和工作温度范围,在晶振应用中还应注意等效串联电阻和负载电容。串联电阻导致晶体的功耗增大。阻值越低,振荡器越容易起振。

负载电容是晶振的一个重要参数,首先,它决定了晶体的谐振频率。一般晶振的标称频率指的是其并联指定负载电容后的谐振频率。应当指出,此处的标称频率是当CL等于指定负载电容时利用公式计算出的值。

因此,晶振的调谐范围与CL值(负载电容)紧密相关。当负载电容值较小时,晶振的调谐范围限制在上端;同样,电容值较大时,调谐范围将限制在下端。负载电容的适当取值取决于晶振的电气特性。

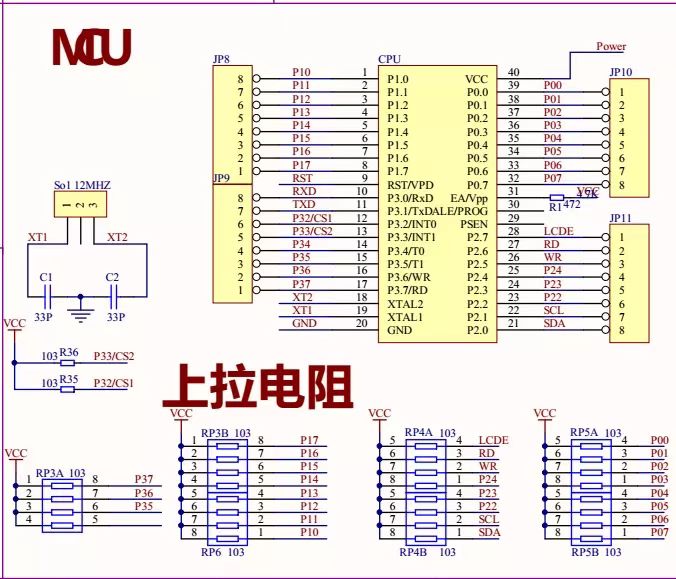

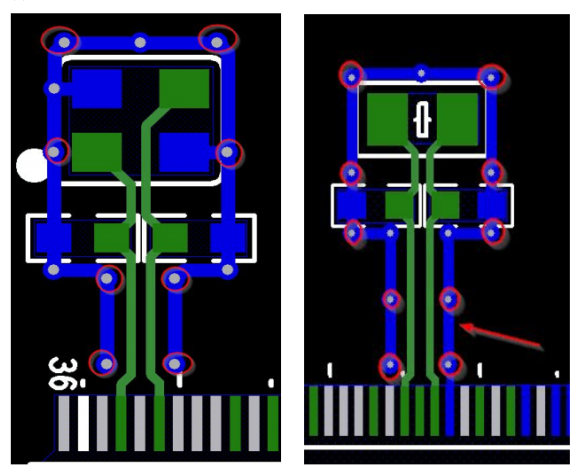

在晶振电路中,为了限制晶振的调谐范围,可通过改变外部并联电容设置向上的调节范围。并联电容取值范围为4-6pf,取决于电路板寄生电容。另一方面,向下的调节范围取决于内部变容 值,不能由外部改变。为了降低寄生电容对向上频率调节范围的影响,在晶振电路板布局中应尽可能的减少晶振引脚对地的寄生电容,保证引脚与地层和层之间的清洁。

了解更多晶振相关资讯,请点击晶诺威官网以下链接:

- 如何减少辐射对时钟信号的干扰?

- 如何降低电磁对晶振时钟信号的干扰

- 晶振频率受干扰的不良现象和解决方案

- PCB晶振布线抗干扰(EMI)设计介绍

- 为何说提供时钟信号的晶振是数字电路的心脏?

- PCB设计中晶振时钟信号电路介绍

- 晶振PCB正确布线需要哪些注意事项?

- 从软件角度看晶振的作用及MCU工作流程

- EMC测试项目及电磁波对晶振的影响

- 晶振位于线路板边缘会带来哪些隐患?

- 晶振受电磁干扰的解决方案

- 晶振到芯片的距离为何越近越好?

- 如何选择高品质晶振生产厂家?

- 晶振振荡电路中负性阻抗到底是什么?

- 你对晶振的激励功率了解有多少?

- 晶振的激励功率怎么设定

- 有源晶振的输出波形分类和应用介绍

- 晶振输出波形和电路形式介绍

- 有源晶振电路设计:如何降低噪音

- 振荡电路的工作原理介绍