通常情况下,在数字电路中,无源晶振频率输入脚和输出脚需要分别外接电容。外接匹配电容可以使晶振输出频率更为精准。如果不外接匹配电容,有可能造成晶振输出频率误差太大,导致实际频率偏移标称频率太多从而造成芯片不能准确抓取到频率信号,误判晶振不起振。在这样的情况之下,建议选择内置补偿电容的晶振。

外接电容的作用是与晶振的负载电容匹配,同时要把电路板产生的杂散电容对晶振频率的影响因素也要考虑进去。这样做的目的是使晶振输出的震荡频率尽可能靠近晶振标配频率,即频率的中心点,比如芯片所需晶振频率为24MHz,意思是说晶振在理想状态应该提供给芯片稳定且精准的24.000000MHz。但在实际晶振产品生产中,基于制造工艺、成本或/及电路板要求等原因,该频点晶振的精度范围一般分为:±10ppm to ±30ppm。

关于晶振精度,当然是越精准越好,这意味着芯片接收到的时钟信号越精准,因此逻辑指令进程越流畅。

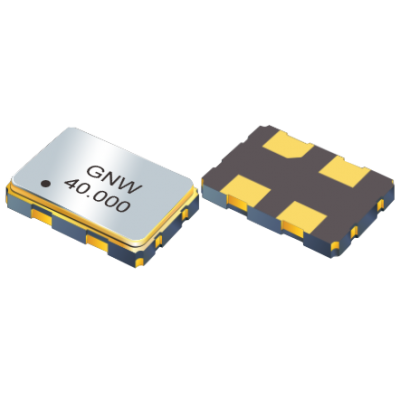

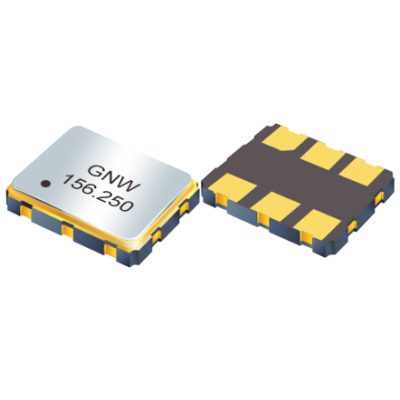

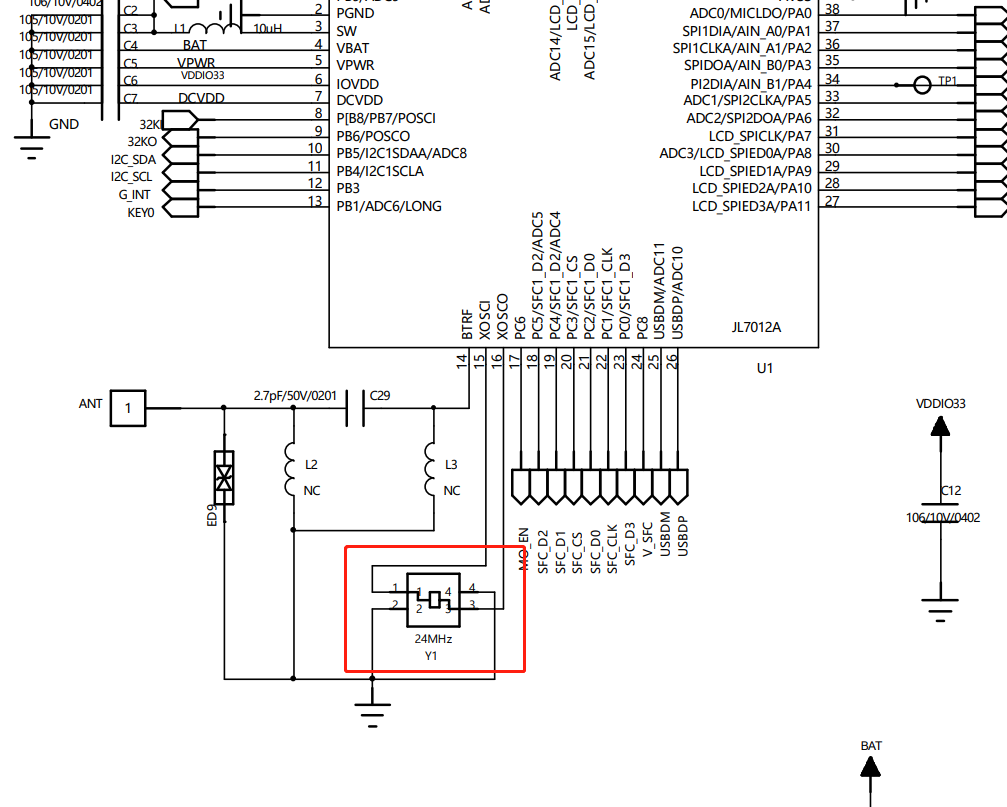

在一些方案中存在不加外接电容的情况,其原因是电路比较简单,PCB走线设计十分合理,PCB上的杂散电容小到可以忽略不计且十分稳定,同时芯片对无源晶振的精度要求并不高。或者晶振已内置补偿电容。如下图所示:

然而,在更多的数字电路方案中,因为晶振发生谐振后,会呈现为纯电阻,即谐振阻抗。在有载谐振中,谐振电阻一般会与负载电容呈反比例关系。也就是说负载电容越小,电路的谐振阻抗越高,就越不容易起振,输出波形幅度就越小。电路中或多或少都会存在杂散电容,当电路振荡时,这些杂散电容便被视为晶体的负载电容进行工作。这些杂散电容过多且不稳定时,就容易导致晶振振荡频率不稳定。在这种情况下,我们很容易误以为是晶振输出频率不够精准而导致“不开机或者开机不良”。这就是我们所说的增加了外接电容的电路会更稳定,时钟频率信号更准确的根本原因。

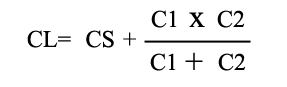

在振荡电路应用中,无源晶振负载电容、杂散电容与外接电容之间的关系示意图如下:

注:

1、 CL: 石英晶体谐振器的负载电容。

2、CS: 指杂散电容,包括IC内部的杂散容值、电路板布线间的电容量、PCB板各层之间的寄生电容等。

3、C1 和 C2:分别指石英晶体谐振器在电路应用中的两颗外接电容。

一般情况下,无源晶振外接电容值选取在10至30pF之间。

了解更多晶振相关资讯,请点击晶诺威官网以下链接: