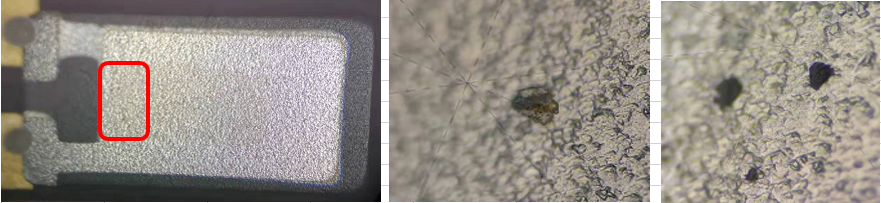

(受污染的石英晶片放大图:异物/杂质导致晶振失效)

晶振在实际电路中,最常见的不良现象为:晶振不起振、频偏及不稳定。排除电路应用因素之外,显然,晶振本身性能不良也占有不少比重。晶振DLD2不良是相对最严重的一种不良现象,将直接导致晶振不起振及/或时振时不振,有效应对措施只有通过重工来更换晶振。

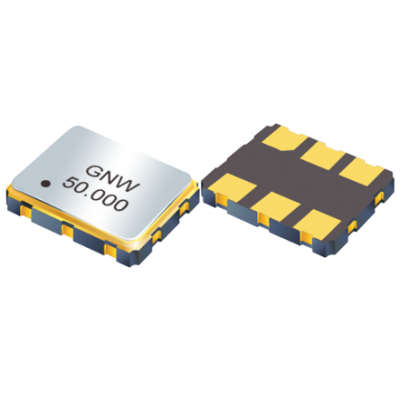

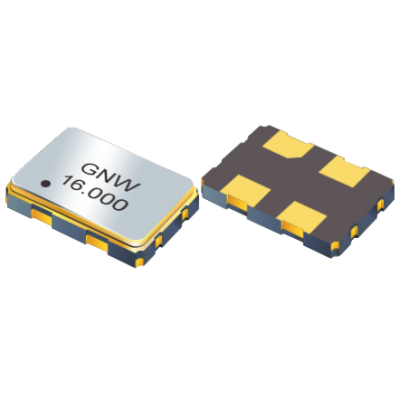

导致晶振DLD2不良的根本原因为晶振产品制程不良。在晶振制造及后续封装整个过程中,车间要求足够洁净,百万级无尘车间达标,晶振内部要求抽真空、充氮气等诸多条件及因素。在没有抽真空的情况之下,即使晶振内部存有极少量水蒸气,一旦当晶振在低温环境下工作,这些水蒸气就可能会凝结成微小的水滴,附着于石英晶片表层,造成晶振严重频率偏差,甚至不起振或时振时不振问题。就更不用说晶振内部存在其它固态尘埃杂质或者有金渣银渣残留在电极上了。晶振内部填充氮气是防止晶振内部金属部件氧化,如石英晶片的镀银电极,有源晶振内部金线与焊盘等,这样做的目的是进一步提升晶振的稳定性及抗老化率。在选择晶振供应商的时候需要对厂商的设备、车间环境、工艺及制程能力予以考量,这关系到产品的品质问题。

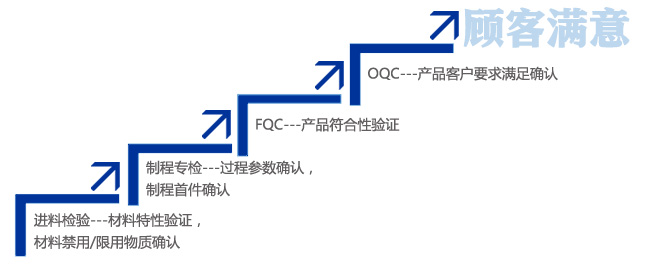

附:晶诺威科技拥有完善的持续改善系统

1、从产品承认阶段开始至产品出货;从过程到检验,制定详细的质量管控计划(FMEA/PCP/SOP/SIP) 。

2、依据制定的管控计划,由各站工程师指导员工的培训,并落实到产线。

3、产线由员工自检(后站管前站);值班长每日生产点检表;制程工程每日参数点检表;设备工程每日设备点检表;质量工程每日质量点检表;主管巡查等一系列的检查方式确保异常的防流出。

4、针对发现的异常,依据纠正的预防单,从产品的围堵,发生/流出原因,发生/流出对策,防止再发等处理方式进行持续改善。

晶振电气参数FDLD 、RLD、DLD2解释说明

FDLD = MaxFr – MinFr在给定的激励功率范围内,测量的最大串联谐振频率与最小串联谐振频率之间的差值。单位是PPM。FDLD 值越小,表明晶振在变化的激励功率下的频率稳定性越好。

RLD = Max R在给定的激励功率范围内,测量的最大电阻值。单位是Ω。较高的 RLD 值可能表明晶振在高驱动水平下的电阻变化较大,可能影响其性能和稳定性。

DLD2 = MaxR – MinR在给定的激励功率范围内,测量的最大谐振电阻与最小谐振电阻之间的差值。单位是Ω。DLD2 值越小,说明晶振的电阻稳定性越好。

关于晶振制造对晶振品质的影响

点胶工艺

导电胶中存在气泡或杂质,导电性能不良;点胶不均匀或胶水量不足,影响其稳定性和可靠性;导电胶的粘度和点胶参数不合适,导致在振动或冲击下性能不稳定。

晶片质量

晶片材料的纯度和均匀性会影响其 DLD 特性。高质量的材料能保持较低的 DLD2 和 FDLD 值。

晶振制造工艺

晶振生产过程中的工艺控制和一致性对 DLD 参数有直接影响。不稳定的制造过程可能导致较大的 DLD2 和 FDLD 值。