尽管在晶振振荡电路设计之前,我们都会从IC方案中获取晶振相关信息,如晶振封装、频率、频差、负载电容、工作电压等,但在晶振实际电路应用中,我们却会遇到一些具体问题,比如按照BOM采购晶振,在电路板上电后,发生晶振不良导致电路板显示不上电或某些功能失效等问题。在不少方案设计中,晶振的作用是进行开机逻辑诊断,这意味着上电开机时,若晶振不起振或严重频偏,必将导致IC无法完成开机诊断程序,进而体现为电路板不上电或无法开机。

在电路板晶振实际应用中,显然如果只依靠IC方案,一旦方案存在设计缺陷,晶振就有可能发生与IC电路不兼容问题,导致晶振不起振现象发生。理论上纸上谈兵,不如实测振荡电路的各项重要参数。这里必须首要提到的就是晶振激励功率和负性阻抗。晶诺威科技就把这两个重要指标计算方式表述如下:

激励功率(Drive Level,简称DL)

指晶振工作时消耗的功率,单位为μW。激励功率太小或太大,都会影响到晶振的正常使用。通常无源贴片晶振激励功率设计参数为10μW ,最大值为100μW。

晶振的实际激励功率实测方法有二:

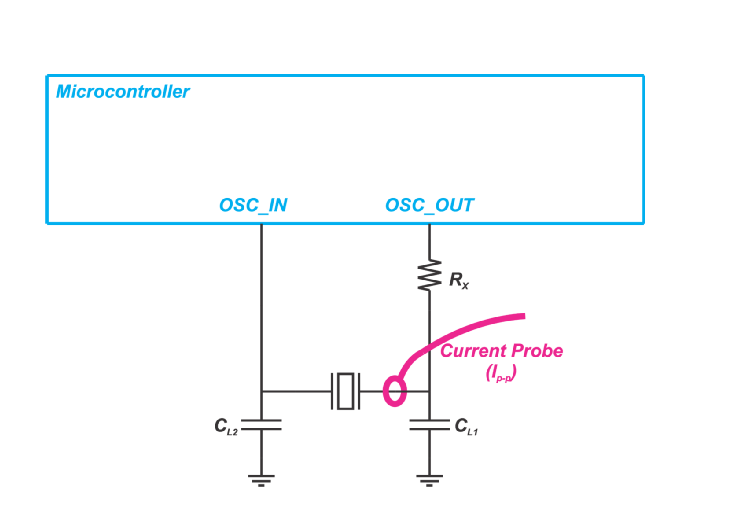

1、用高频电流探头测试晶振工作电流来计算:

DL= I^2 * RL

RL= RR(晶振阻抗)*(1+C0/CL)^2

C0:静电容

CL:负载电容

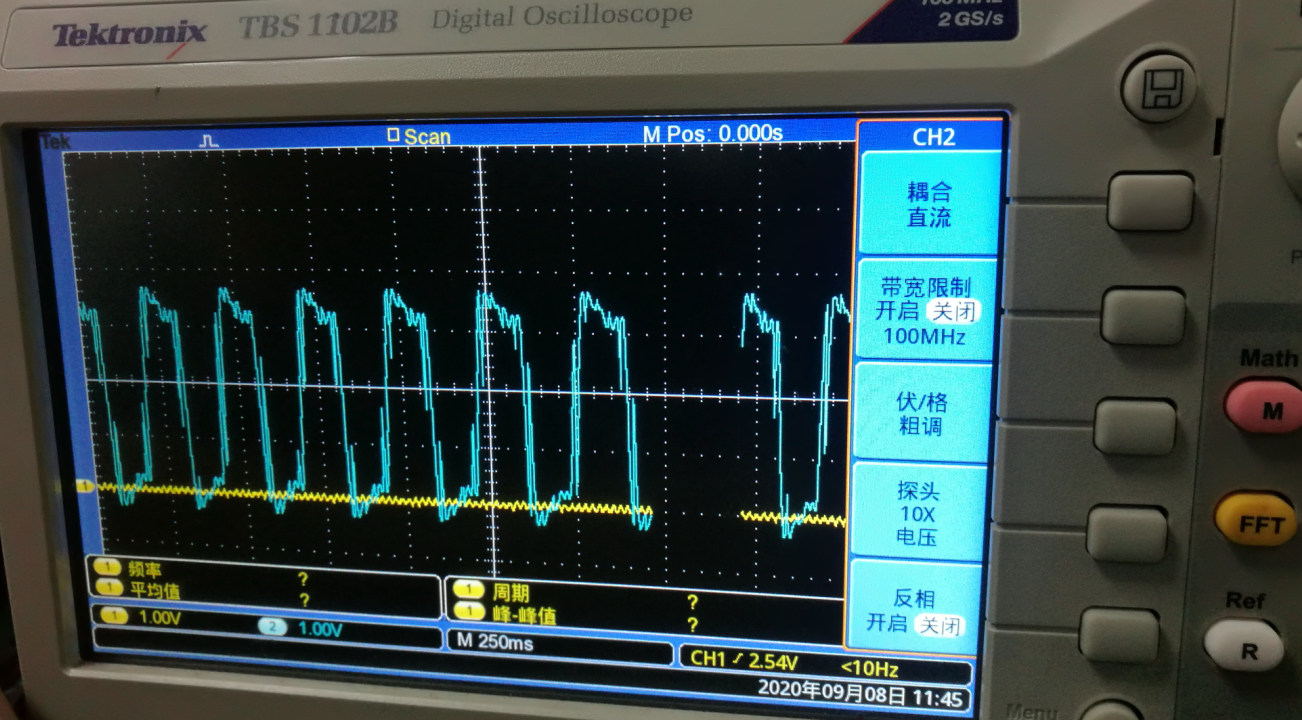

2、用高阻电压探头测试振荡信号幅度后计算:

DL=P=(V^2)*R/(Z^2) 其中V=(Vppout+Vppin)/2*2^0.5

Z=(R^2+X^2)^0.5; R=R1*(1+C0/CL)^2; X=1/ωCL

激励功率原则:

确保晶振起振并在晶振正常工作中各项电气参数正常。

负性阻抗(Negative Resistance)是来判断振荡电路稳定性的一个重要参数,通常表示符号为-R,单位为Ω。负性阻抗太小,会直接影响晶振是否起振,负性阻抗太大则会造成晶振跳频或损坏。从经验推理,负性阻抗取值不能小于晶振阻抗5倍。

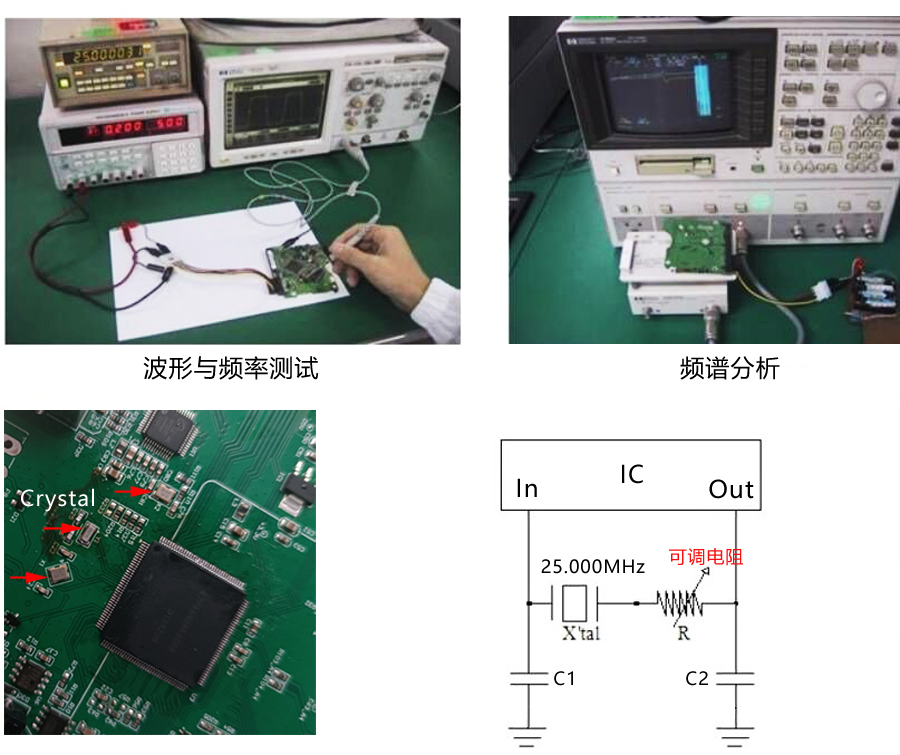

负性阻抗的实测步骤如下:

1、将可调电阻与晶振串联接入回路

2、调节可变电阻Vr使回路起振或停振

3、当回路刚停振时测试Vr

4、得到负性阻抗值│-R│= R1+Vr

注:

R1:晶振的阻抗值

Vr:可变电阻

负性阻抗值计算公式:│-R│> 5 * (R1+Vr)