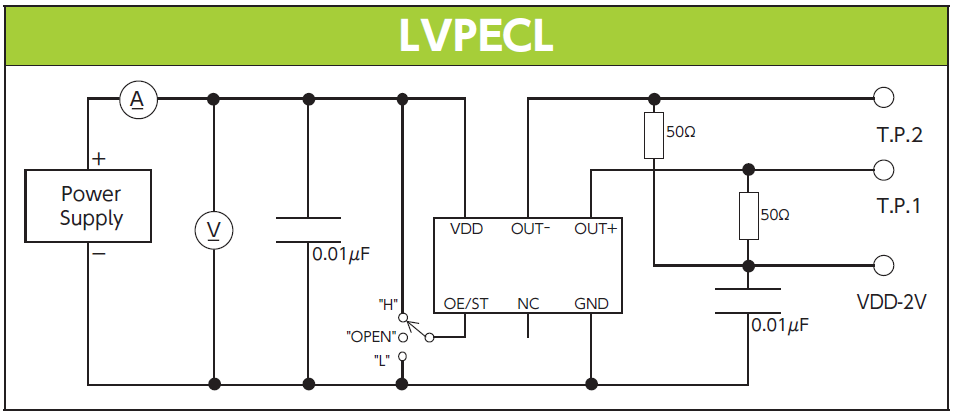

差分晶振LVPECL 输出波形介绍如下:

LVPECL

英文: Low Voltage Positive Emitter-Couple Logic

中文:低电压输入发射极耦合逻辑

LVPECL输出逻辑属于方波,输出功率比较大,驱动能力较强,但谐波分量非常多,该输出模式属于差分晶振的输出逻辑。

PECL代表“发射极耦合逻辑”,PECL是常用于高速时钟分配电路的差分逻辑输出,PECL需要+5V电源。低电压PECL(LV PECL)表示PECL电路设计用于3.3V或2.5V电源,电源电压与低压CMOS石英晶振相同。PECL 是由ECL 演变而来的,ECL 即Emitter-Couple Logic,也就是发射极耦合逻辑。

ECL 有两个供电电压VCC和VEE。当VEE接地时,VCC接正电压时,这时的逻辑称为PECL;当VCC 接地时,VEE接负电压时,这时的逻辑成为NECL,VEE一般接-5.2V电源;一般狭义的ECL 就是指NECL。由于PECL/LVPECL可以和系统内其他电路共用一个正电源供电,所以PECL/ LVPECL相对于ECL应用更为广泛。起初的PECL器件是将VCC接+5V,后来为了直接利用广泛使用的3.3V和2.5V电压,出现了VCC=3.3V/2.5V的LVPECL(Low Voltage PECL)。

LVPECL在不同电平之间不能直接驱动,需要使用交流耦合,电阻网,特供芯片等来过度,但是由于都是射随结构,所以必须利用电阻调节到一个直流偏置电压。

LVPECL电路是一种非饱和型的数字逻辑电路,电路内晶体管工作在线性区或截止区,速度不受少数载流子的存储时间的限制,所以它是现有各种逻辑电路中速度最快的一种, 能满足高达10Gbps工作速率。