在有源晶振的电路应用中,我们该如何尽量避免其对电源的干扰呢?

晶诺威科技建议PCB设计如下:

1、晶振外壳接地设计,目的是防止晶振信号的向外辐射,同时屏蔽外来杂波干扰。

2、晶振所在层铺地设计,目的是防止晶振信号干扰其它层。

3、建议晶振下面不要布线,其周围5毫米范围内不要设计布线及安置其它电子元件。

4、建议不要在电路板边缘设计安置晶振,以防止短路。另外,若晶振位于电路板较边缘的位置,晶振与参考接地板的电场会被PCB板的GND分割,造成参考接地板电场大大减小。

5、建议时钟信号线越短越好。

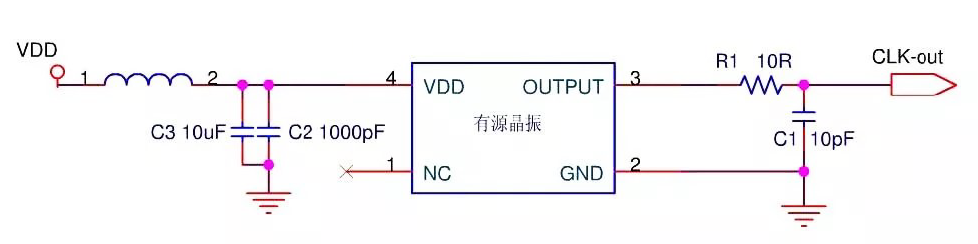

有源晶振EMC设计,如下图所示:

1、晶振电源去耦非常重要,建议加磁珠,去耦电容选两到三个,容值递减。

2、晶振时钟信号输出脚位加匹配电阻,具体匹配阻值基于实测结果而定。

3、预留的电容C1电容值要小,目的是构成一级低通滤波。请根据具体测试结果选择电阻及电容。

注:

- R1为预留匹配设计,可根据实测情况进行调整或更换磁珠。

- C1为预留设计,可根据实际情况增加或调整。