一般晶振频偏主要发生在无源晶振的实际应用中。一旦频偏严重超差,极有可能会造成整机不上电或系统无法运行。

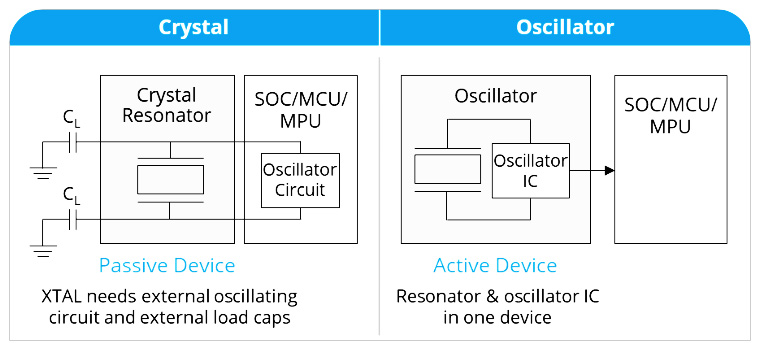

晶振分为无源晶振和有源晶振两种。无源晶振需要电路匹配,单体无法起振。有源晶振本身已拥有包括IC在内的一套匹配好的振荡电路,因此无需担忧频偏只需选择满足时钟芯片所需频率精度的有源晶振产品即可。

造成无源晶振频偏的因素主要由以下三个方面:

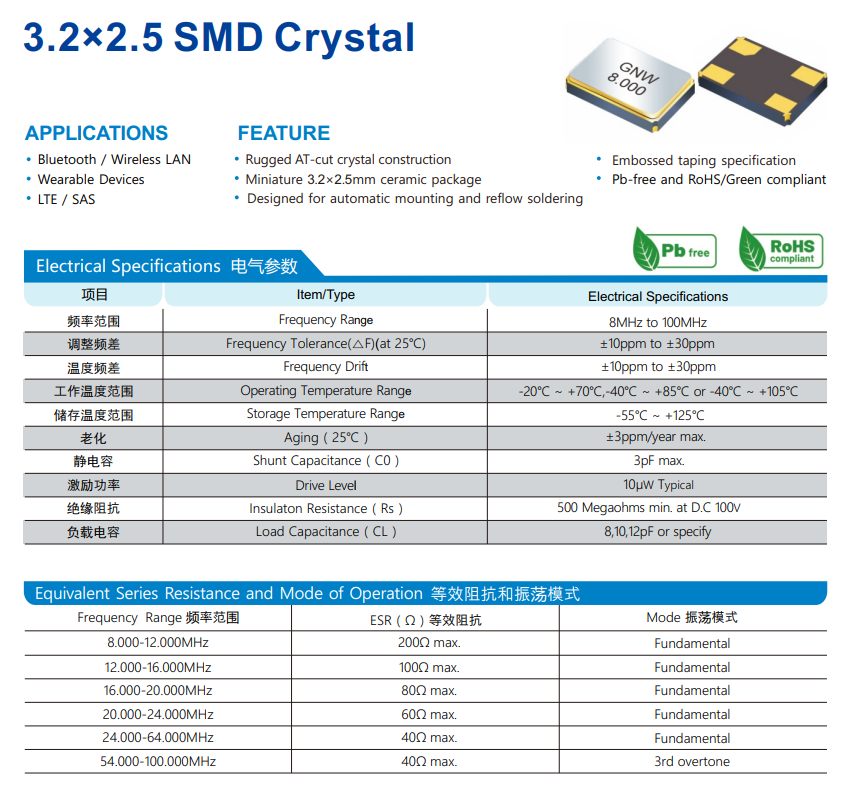

1、晶振品质,即晶振本身品质必须符合要求,比如调整频差、温度频差、年老化率等参数在晶振实际工作中必须满足时钟芯片要求。

举例:一款时钟芯片对晶振的参数要求如下:

调整频差(Frequency Tolerance): ±10PPM ,工作温度默认为:25℃±2℃

温度频差(Frequency Temperature Characteristics): ±10PPM ,指定工作温度:-40℃~+85℃

频率年老化率(Frequency Aging Rate): ±3ppm/ 年

显然,温度及时间对晶振频偏存在影响。

2、晶振的外接电容

无源晶振本身具有一个重要参数,叫作“负载电容”,而在电路实际应用中,我们往往为无源晶振的频率输出脚与输入脚分别串联一颗等值的电容元件,我们称之为“外接电容”。外接电容的作用是对晶振实际输出频率进行微调。比如,若晶振输出频率偏正,我们则酌量下调外接电容值。反之,若晶振输出频率偏负,我们则微微上调外接电容值。

若外接电容与晶振没有匹配好,会直接导致晶振频偏发生,这也是无源晶振在实际应用中最为常见的问题。

值得提醒的是,对外接电容的调整,只是起到对晶振实际输出频率精度的微调作用。若晶振频偏严重,外接电容调节失效,则建议选择频率精度更高的无源晶振。

3、杂散电容

杂散电容因电路板走线的设计方式及电路板本身的复杂程度相关。若晶振周边电路存在过多杂散电容,就等同于在外接电容的基础上又增加了电容。因此当杂散电容发生变化时,如我们经常提及的“用手摸一下晶振”,或“用热吹风吹一下晶振”,晶振就又起振了,或又不振了等现象,基本上都是因为杂散电容发生了变化导致晶振实际输出的频率受到了影响。换句话说,若晶振处于频率范围边缘值(即时钟芯片捕捉的晶振频率范围的临界值)时,最容易受到杂散电容的直接影响。那么,如何判定晶振已经发生频偏?最直接的方式就是给电路板上电,使用频率计测量晶振的实际频率输出。根据晶振实际频偏程度,调整外接电容使输出频率尽可能靠近频率中心点。另外,做好对晶振的屏蔽,减少周边电路对晶振的干扰。

如何最大化程度地减少晶振频偏的影响?

1、选择温度系数较低的晶振,可以减小温度变化对晶振频率的影响。

2、确保电源电压稳定,避免过高或过低的电压影响晶振的频率。

3、根据实际应用情况,选择合适的负载阻抗,确保晶振能够正常工作。

4、将晶振安装在正确的位置,尽量靠近IC信号管脚且确保其不受震动的影响。同时,在安装时可以采取一些措施来减小应力对晶振的影响,如使用橡胶垫等。

5、对于需要高精度时钟信号的应用,可以定期对晶振进行校准,以确保其频率的准确性。

通过上述措施,我们可以较大程度地减小晶振频偏的影响,提高系统的稳定性和准确性。当然,在实际应用中,我们还需要根据具体的情况和需求,灵活采用不同的方法来解决问题。