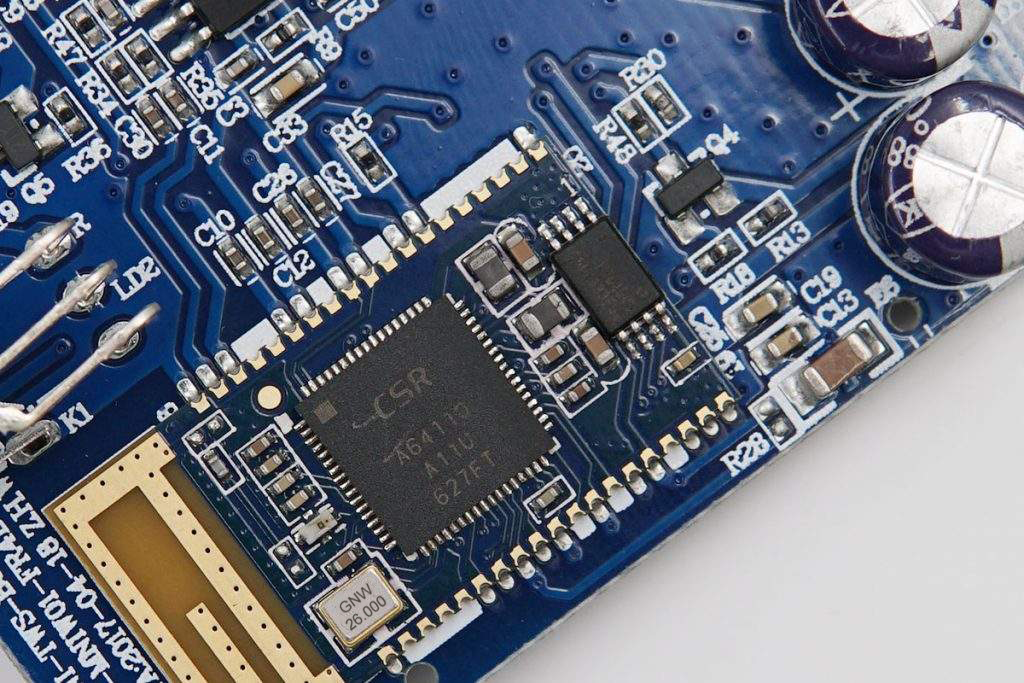

振荡电路用于实时时钟RTC,对于这种振荡电路只能用32.768KHz的晶振,晶振被连接在OSC3与OSC4之间而且为了获得稳定的频率必须外加两个带外部电阻的电容以构成振荡电路。

32.768KHZ的时钟晶振产生的振荡信号经过石英钟内部分频器进行15次分频后得到1HZ秒信号,即秒针每秒钟走一下,石英钟内部分频器只能进行15次分频,要是换成别的频率的晶振,15次分频后就不是1HZ的秒信号,时钟就不准了。32.768K=32768=2的15次方,数据转换比较方便、精确。

(一)14级二进制串行计数器/分频器CC4060由两部分组成,一部分是14级分频器,另一部分是振荡器。振荡器外接用电子表的石英晶振,构成频率为32768Hz(=215)的振荡器,32768Hz经过CC4060十四级分频后为2HZ,再经过一个D触发器组成的T’触发器二分频,就得到1Hz秒信号,D触发器选用74LS74。电路如图5所示。其中R2为直流负反馈电阻,使CC4060内部与非门工作于传输特性的线性转折区,本例取2MΩ。C6,C7用于稳定振荡,本例取100pF。R1C5组成上电复位电路,在接通电源瞬间产生一个微分脉冲,使CC4060输出清0,分别取10kΩ、10µF。

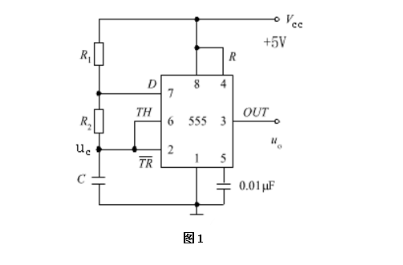

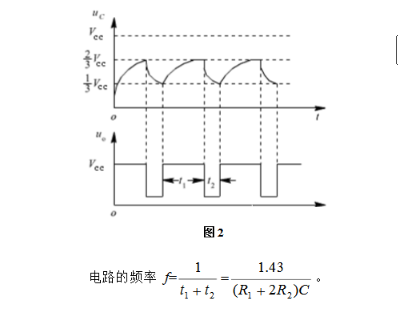

二)555定时器构成多谐振荡的秒信号产生电路555定时器是一种集模拟、数字于一体的中规模集成电路,其应用极为广泛。利用它可以很容易地接成施密特触发器、单稳态触发器和多谐振荡器,秒信号产生电路多为555定时器。

工作原理:接通电源后,电容C被充电,当uc上升到2/3Vcc时,使uo为低电平,同时放电三极管T导通,此时电容C通过R2和T放电,uc下降。当uc下降到1/3VCC时,uo翻转为高电平。电容放电所需时间为:t2=R2Cln2≈0.7R2C;电容充电时间t1≈(R1+R2)Cln2≈0.7(R1+R2)C

本例选用R1=R2=10KΩ,C选47µF。即可在输出端uo得到频率为1Hz的秒时钟信号。本电路调节电阻R1可以调节频率,可调节占空比。缺点是由于占空比是可调的不是标准的方波,波形失真较大,且频率的稳定性差。适用于频率精度要求不高的工作场所。

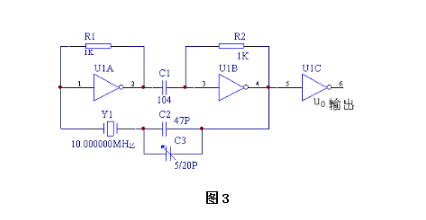

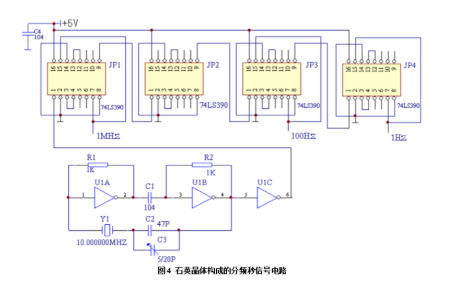

(三)石英晶振主要成分是二氧化硅,它的物理化学性质十分稳定,Q值很高,可达104~106,选频特性非常好,构成的振荡器电路有一个极为稳定的串联谐振频率。电路的振荡频率取决于石英晶振的振荡频率。本例用二级反相器与石英晶振组成多谐振荡器。R1、R2的作用是使U1A、U1B工作在线性放大区,C1的作用是正反馈耦合,晶振的作用是选频。本例的选用的晶振频率是10.000000MHz的晶片。因此本振荡器的频率为10.000000MHz。

要获得1Hz的秒信号必须要对10MHz的晶振信号进行多次分频,可采用74LS390双十进制计数器进行分频,图4是石英晶振构成的分频秒信号电路。本电路的显著优点是频率稳定性极好,可达1.000000Hz的精确度,若想得到高的频率稳定度,可采用辅助温度补偿电路,10.0MHz的频率稳定度可达到1-2个PPm,且波形失真小。该电路适用于对秒信号要求十分严格的电路中,如高精度数字式频率计中的计数闸门。

四)用单片机产生标准秒信号的优点是硬件电路简单,可靠性好,输出波形好,且频率稳定度与晶振相同。但由于是利用单片机内部的计数器进行自动计数器,且必须靠“中断”服务程序来实现秒信号的生成,由于CPU对中断响应时间的不确定性的关系,因而每个秒周期均存有数微秒的时间延迟,倘若对其进行适当的软件补偿并反复进行修正调试,也可使延迟时间减至最小,从而也可获得更加精确的秒信号,且可获得晶振级的频率稳定度。