关于无源晶振起振电路中的负性阻抗测试方法,晶诺威科技介绍如下:

负性阻抗概念

英文:Negative Impedance/Negative Resistance

指振荡电路需要满足无源晶振起振并保持稳定输出频率的阻抗特性值。我们通常参考无源晶振的两个功能性引脚(频率输出脚与频率输入脚)朝向的振荡电路。

需要指出的是,负性阻抗并不是石英晶振本身的电气参数,但却是振荡线路的一项重要特性参数。负性阻抗会受到晶振两端的外接电容以及晶振匹配后整体电路板杂散电容的影响。而晶振起振是由于电路中的噪音所引起。其原理是,随着谐振增加,且逐渐达到稳定的无源晶振频率和一定的振荡幅度,这就是我们称之为的谐振(共振)。

简而言之,噪音是杂乱无章的振荡频率,而晶振频率则是稳定的频率。其最终结果就是晶振的频率会从众多繁杂频率中脱颖而出。因此,晶振的频率稳定性是关键,比如避免跳频。而负性阻抗则特指在晶振起振时振荡频率的阻抗特性值。负性阻抗值越大,晶振越容易起振。一般电子产品的负性阻抗要求大于3~5倍的晶振阻抗。

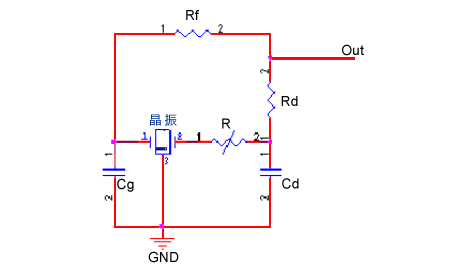

负性阻抗测试方法具体操作如下:

1)先在无源晶振回路中加一个可变电阻R

2)起始R=0,然后慢慢加大R,直到示波器无波形输出

3)记录R值

4)与常温阻抗特性比较,要求>5倍,完成匹配