(有源晶振引脚英文定义)

(有源晶振引脚定义)

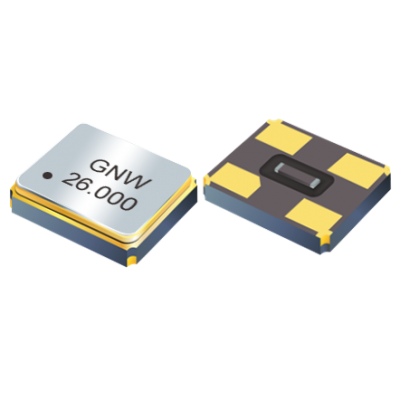

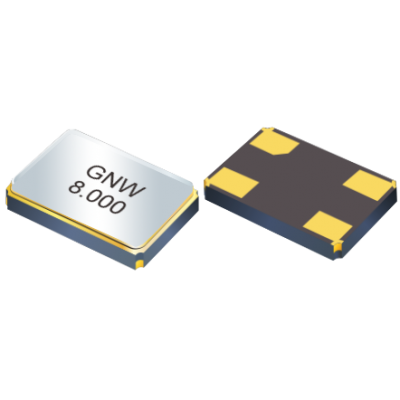

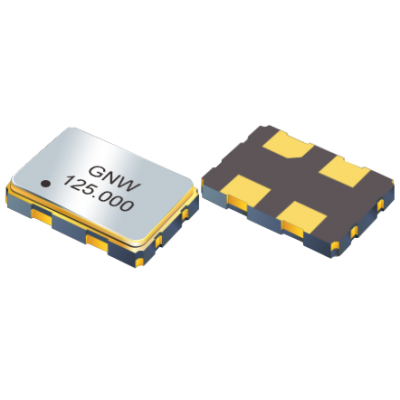

(晶诺威科技有源晶振产品图)

通常,数字系统采用0和1表示的二进制。但在一些特殊应用中,需要第三状态(Hi阻抗输出)。TTL,HCMOS或HCMOS有源晶振提供三态输出或三态启用/禁用功能(Tri-state,N/C)。其常见应用包括自动测试,总线数据传输。

这三种状态是低,高和高阻抗(HiZ或浮动)。高阻抗状态的输岀表现得好像它与电路断开,除了可能有小的漏电流。

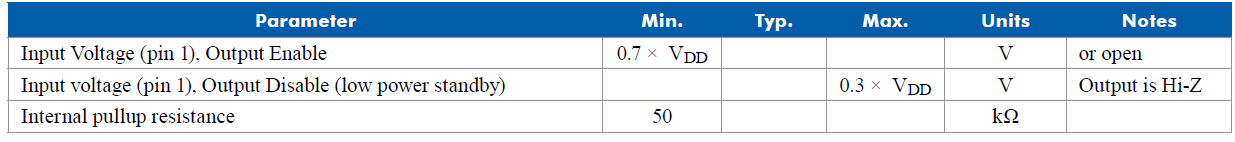

三态器件具有使能/禁止输入,通常在几乎任何封装的引脚1上。当使能为高电平或悬空时,器件振荡(输出高电平和低电平),当引脚1接地(逻辑“0”)时,器件进入高阻态。

总线是一组通用的电线,通常用于数据传输。三态总线有几个三态输出连接在一起。通过控制电路,除了一个总线上的所有设备都具有高阻抗状态的输出。其余器件使能,驱动高低输出总线。

三态功能的其它应用是用于自动测试设备(ATE)。几个有源晶振输出连接在一起。对于控制电路,除了振荡器外,所有振荡器都具有高阻抗状态的输出。选择的振荡器将从计数器读出其频率。

在三态函数生效之前总会有一些延迟。此转换发生在两个转换(禁用和启用时)。从低电平开始的三态输出禁止时间是tPLZ,三态到低电平的输出使能时间是tPZL。

CMOS

上升和下降时间CMOS技术的上升和下降时间取决于其速度(CMOS、HCMOS、ACMOS、 BICMOS),有源晶振的电源电压,负载电容和负载配置。CMOS 40000列的典型上升和下降时间为30ns, HCMOS为6ns,而ACMOS( HCMOS/TTL兼容)的最大上升和下降时间为3ns。典型的上升和下降时间在其波形水平的10%至90%之间测量。

ACMOS输出终止技术

由于ACMOS( HCMOS/TL兼容)器件的快速转换时间,在测试或测量有源晶振电气性能特性时必须使用正确的端接技术。端接通常用于解决电压反射问题,这实质上导致时钟波形中的步骤以及过冲和下冲。这可能导致数据错误时序及更高EM和噪声。

由于PCB板上的线长度及其负载配置,还需要端接。有两种终止时钟轨迹的通用方法,即将器件的输出阻抗与线路阻抗相匹配的过程:

方法1:串联终端在串联终端中,阻尼电阻靠近时钟信号源放置。Rs的值必须满足以下要求:Rs≥ZT-Ro

方法2:上拉/下拉电阻在上拉/下拉终端中,组合的戴维宁等效于迹线的特征阻抗。不会产生任何反射,同时降低EMI。

在具有三态Tri-state功能的有源晶振中,晶振输出可由三态引脚控制:

逻辑高:输出支持

逻辑低:输出禁用

三态功能将允许输出引脚承担高阻抗状态,有效地消除振荡器输出的电路。

振荡器电路可以保持或关闭,而输出在三态被禁用。

三态振荡器工作模式:振荡器电路关闭

优点:待机电流较低

缺点:启动时间较长

(基本模式>0.2mS)

(三次泛音模式>2mS)

三态振荡器工作模式:振荡器电路开启

优点:允许输出时间短

缺点:更高的待机电流

如何禁用三态Tri-state功能

如果不需要三态Tri-state功能,建议三态引脚悬空。