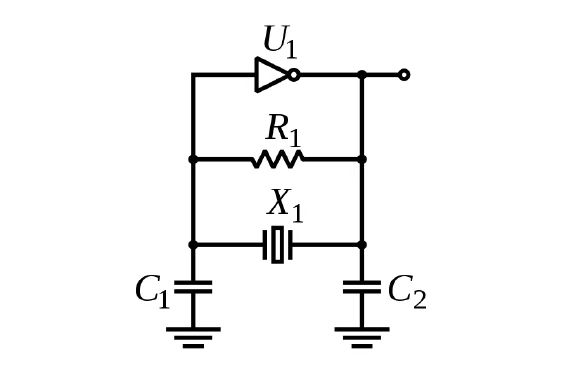

首先说明的是:但凡需要外接电容的晶振均为无源晶振。另外,注意区分外接电容C1和C2(接地电容,对地电容)并不等同于晶振负载电容(CL)。C1和C2是电路板和包括IC 和晶振在内的组件的总电容值。

一般情况下,增大无源晶振的外接电容将会使晶振振荡频率下降,即偏负向。举例,若无源晶振12MHz的外接电容为18PF,实际输出频率为12.002876MHz。更改外接电容为27PF之后,该晶振的实际输出频率会有所降低,如:11.9998923 MHz。

晶振的外接电容越大,晶振的振荡越稳定,但是会增加起振时间,即晶振起振慢,其原理是外接电容会存储更多电荷,即降低电流强度,从而降低电路提供给晶振起振的激励功率。

当无源晶振的输出波形出现削峰、畸变时,这一般是由于电流过驱动(over drive)导致,可以尝试通过串联一颗电阻解决,电阻值一般在几十kΩ~几百kΩ。如果要稳定波形,则可尝试并联一颗1M反馈电阻。

晶振电路应用注意事项

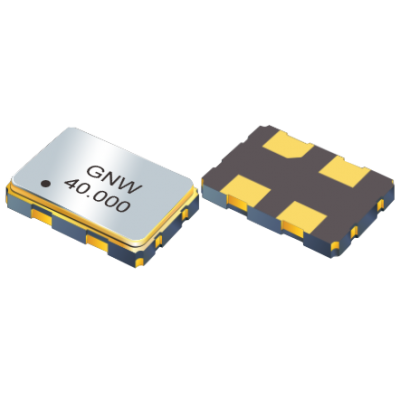

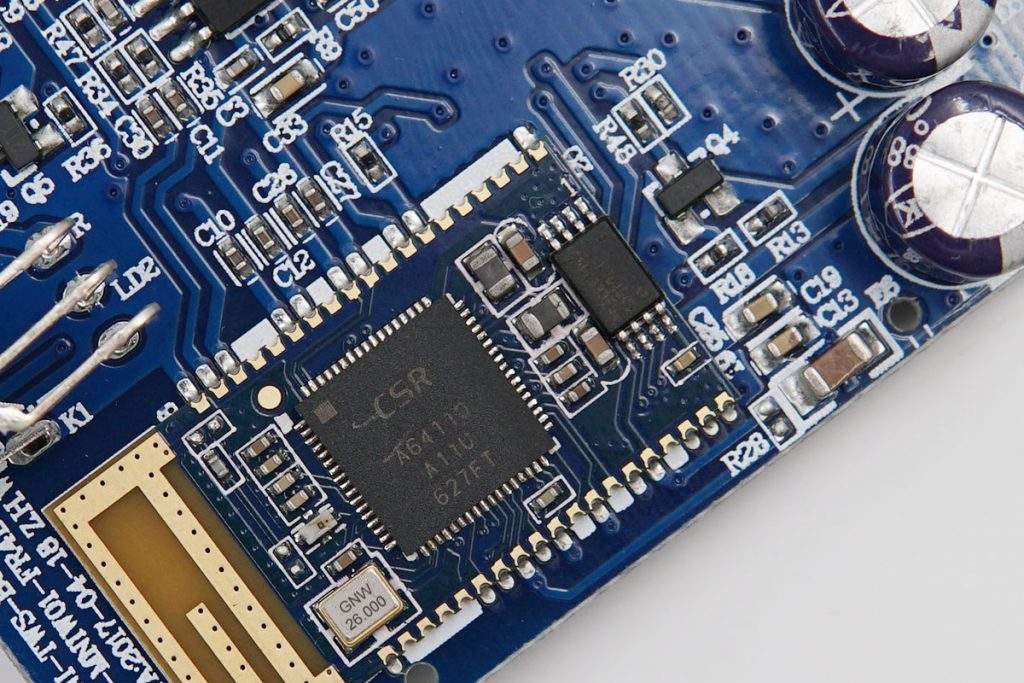

![]() 晶振布局:晶振电路应尽量远离干扰源,如电源、高频信号等,以免影响晶振的稳定性。

晶振布局:晶振电路应尽量远离干扰源,如电源、高频信号等,以免影响晶振的稳定性。

![]() 电容选择:晶振电路中的电容应选择合适的数值,以保证晶振的稳定性和工作频率。

电容选择:晶振电路中的电容应选择合适的数值,以保证晶振的稳定性和工作频率。

![]() 阻尼电阻:为了提高晶振电路的稳定性,可以在晶振电路中加入适当的阻尼电阻。

阻尼电阻:为了提高晶振电路的稳定性,可以在晶振电路中加入适当的阻尼电阻。