串联电阻降低晶振相噪(phase noise)避免输出波形(output waveform)失真方法介绍

主要分为连接串联电阻与连接终端电阻两部分:

- 连接串联电阻:

晶振连接输入对象的元器件时,通常产生过冲、下冲或振铃等波形变形。这些变形的波形中含有振荡频率的约3-7倍的射频成份,将引发相噪,所以必须去除。为了去除射频成份,应在晶振的输出端与输岀线路之间连接串联电阻。所插入的电阻值(Rs)等于输岀线路的阻抗(Z0)与晶振的输岀阻抗(R0)之差。

串联电阻最佳值亦可通过实验得岀。实验方法是一边用示波器等观察输出波形,一边把串联电阻值从小逐渐调大,得岀过冲、下冲或振影等消失时的电阻值。

- 连接终端电阻:

终端电阻是否连接取決于所使用的数字或模拟信号种类,以及输岀波形的时钟线的种类。

输岀波形的失真一般出现在输岀线路的阻抗与输入对象元器件的输入阻抗不匹配的情况之下。非匹配状态的行进波在输入端被反射后,反射波与行进波相重叠使输岀波形出现紊乱,从紊乱部分产生高频率的相噪。将晶振的输岀分支传送到多只元器件使用时,上述波形失真或引起触发误差。因此阻抗匹配十分重要。

为了防止从输入端的反射,应当接终电阻使输入端的阻抗等于输岀路线的阻抗。

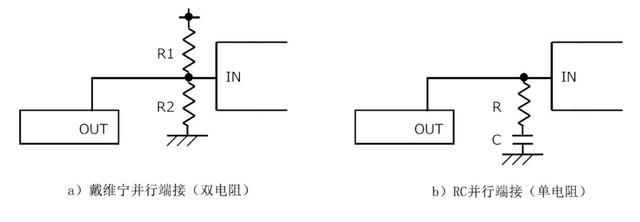

注:可分为单电阻和双电阻。如下图所示: