晶振周围电路的合适设计对减少相噪noise极为重要。只要电路设计妥善适宜,即可很大程度避免相噪问题,从而充分发挥电子元器件本身所具有的性能。

减少晶振周边电路相噪的方法主要有以下两点:

- 缩短输岀线路

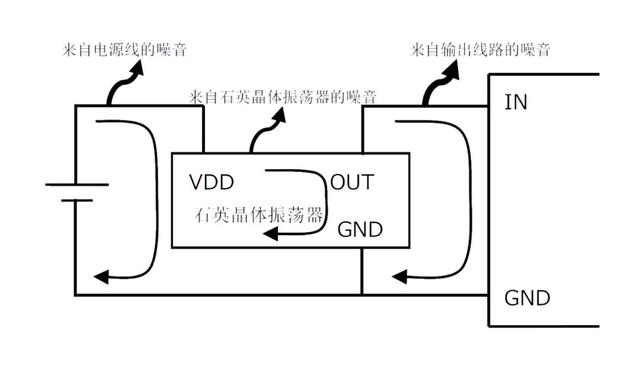

输出线路是电路中最容易释放相噪的部分。为此,在设计电路图案之际,应当最优先设计输岀线路部分,采用长度最短、无阻抗变动的最佳输出线路图案。缩短后的输出线路布线的谐振频率将变得高。输出的信号随频率增大而衰减,从而可以达到减少相噪释放之目的。

- 缩小电流环路

来自输出线路的相噪释放量与电流环路的大小成正比。因此,必須尽量缩短晶振和输入元器件的输出线路与接地线长度,故而亦可采用在输岀线路的背面印制接地线的方法。