在晶振应用中,什么是抖动和相位噪声?

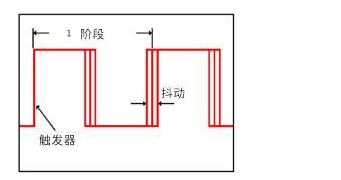

抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的 bit 周期都非常短,一般在几百 ps 甚至几十 ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

实际信号可能具有较高复杂性,比如既有随机抖动成分(RJ),也有不同频率的确定性抖动成分(DJ)。确定性抖动可能由于码间干扰或一些周期性干扰引起,而随机抖动很大一部分来源于信号上的噪声。一般我们把数字信号超过阈值的状态判决为“1”,把低于阈值的状态判决为“0”,由于信号的上升沿不是无限陡的,所以垂直的幅度噪声就会造成信号过阈值点时刻的左右变化,这就是由于噪声造成信号抖动的原因。

要进行信号抖动的分析,最常用的工具是宽带示波器配合上响应的抖动分析软件。示波器里的抖动分析软件可以方便地对抖动的大小和各种成分进行分解,但是现在很多高速芯片对时钟的抖动要求都在 1ps 以下甚至更低。这就需要借助于其它的测量方法,比如相位噪声(phase noise)的测量方法。

相位噪声:

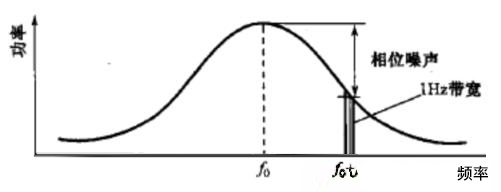

在频域上,数据偏移量用相位噪声来定义。对于频率为f0的时钟信号而言,如果信号上不含抖动,则信号的所有功率应集中在频率点f0处,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。信号的相位噪声,就是信号在某一特定频率处的功率分量,将这些分量连接成的曲线就是相位噪声曲线。相位噪声通常定义为在某一给定偏移处的dBc/Hz值,其中dBc是以dB为单位的该功率处功率与总功率的比值。如一个振荡器在某一偏移频率处的相位噪声定义为在该频率处1Hz带宽内的信号功率与信号总功率的比值,即在fm频率处1Hz范围内的面积与整个噪声频率下的所有面积之比。

(信号相位噪声曲线图)

从相位噪声曲线图可知,绝大多数抖动都集中在频率f0附近,距离f0越远的频段,抖动能量越小。

以下面的例子为例,说明对时钟输入的要求:

RMS JPER(12kHz~20MHz):0.5ps

相位噪声(10~100kHz):-120dBc/Hz

这实际上是两个要求,一个是要求在频段12kHz~20MHz内,均方根抖动不能大于0.5ps;另一方面要求在频段10~100kHz内,任何频点处的功率谱密度都不能超过-120dBc/Hz。

拓展阅读:相位噪声对信号质量及稳定性的影响

在许多系统中,相位噪声是一项至关重要的参数。特别是在高性能雷达系统中,这个参数尤为关键,因为高性能雷达系统需要可靠地侦测来自目标的极微弱返回讯号。当相位噪声越低时,这些返回讯号的清晰度更高,侦测范围也相应增大。 对于数字系统而言,相位噪声的存在被视为抖动,并对系统性能产生直接影响。当相位噪声越低时,抖动程度降低,系统的稳定性和性能也相应提升。同样地,通讯系统将相位噪声视为对讯号带宽的一种影响,较低的相位噪声意味着更小的抖动,这进一步意味着更低的所需带宽,从而有助于优化通道宽度和节省资源。