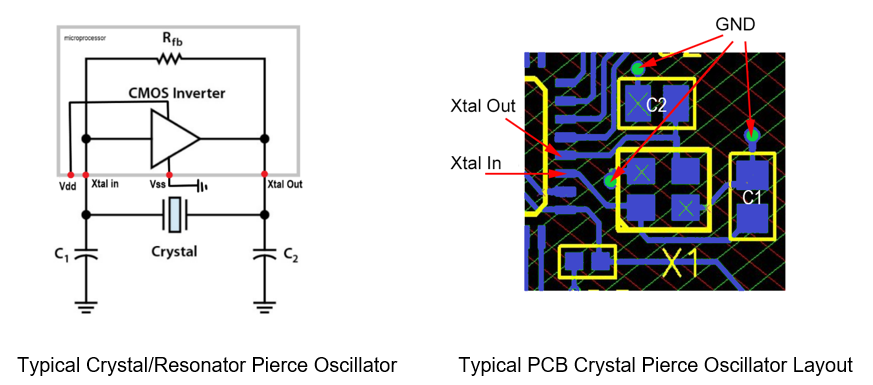

无源晶振及两颗外接电容在PCB的位置

- 两颗外接电容应尽量靠近晶振引脚(频率输入脚与频率输出脚)设计。

- 晶振核心部件为石英晶体,容易受外力撞击或跌落影响而破碎。在PCB布线时最好不要把晶振设计在PCB边缘,尽量使其靠近芯片。

- 晶振走线需要用GND保护稳妥,远离敏感信号源,如RF及高速信号,以免频率信号受到干扰。

- 晶振位置远离热力源,高温会造成晶振频率偏差,因为石英晶体具有“温漂”物理特性。

关于外接电容(C1&C2)与晶振负载电容CL匹配

- 晶振负载电容计算公式: CL=C1*C2/(C1+C2)+Cic+Cp

- C1和C2为晶振两脚外接电容,又被称为匹配电容或对地电容。

- Cs(即Cic+Cp)为PCB板寄生电容,一般理论上按照3~5pF计算,但在应用中需视实际情况而定。

外接电容值大小一般取C1=C2=2CL,即:同值。这样并联起来会更加接近负载电容CL。在一般情况下,适当增大外接电容会使晶振振荡频率下降,而适当减小外接电容则会使晶振振荡频率升高。补充一句,调节外接电容大小只能对晶振输出频率起到微调作用。

拓展阅读:晶振位置

电磁辐射干扰电磁辐射是指电流通过导线时产生的电磁场向周围空间传播的现象。当晶振放置在PCB边缘时,由于距离较近,其容易受到其他电路元件产生的电磁辐射的干扰。这种干扰会导致晶振频率的偏移,进而影响整个电路的稳定性和可靠性。

机械振动干扰PCB边缘处往往存在机械振动的可能,例如设备的震动、外界的冲击等。晶振作为一种微小而脆弱的元器件,对机械振动非常敏感。如果晶振放置在PCB边缘,其容易受到机械振动的影响,从而导致晶振频率的变化,进而影响整个电路的正常工作。

温度变化干扰PCB边缘处与外界环境接触更为紧密,因此容易受到外界温度的影响。晶振的工作稳定性和频率都与温度密切相关。如果晶振放置在PCB边缘,其容易受到外界温度变化的干扰,从而导致晶振频率的偏移,进而影响整个电路的性能。