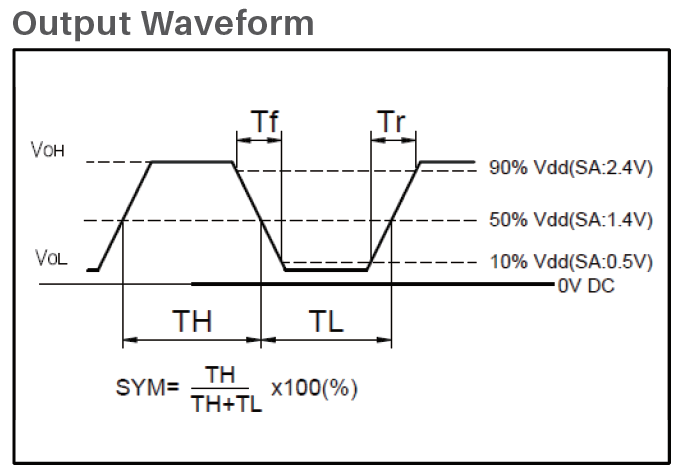

有源晶振常见输出方式(output waveform)图例

有源晶振常见输出方式(Output Waveform)如下:

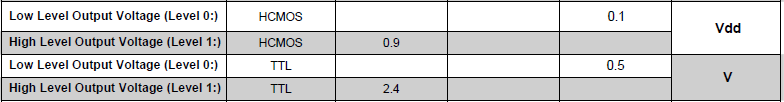

CMOS

CMOS是Complementary Metal Oxide Semiconductor的英文缩写,这种接口电平标准的初衷是用于基于NMOS、PMOS组成的MOS管结构的数字系统之间的。

工作于CMOS接口标准下的数字电路,其内部有源晶振的标准电源供给为5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于4.45V,状态0的电压要求为小于等于0.5V;

对于输入端,状态1的判定要求为大于等于3.5V,状态0的判定要求为小于等于1.5V。

CMOS与TTL接口相比,有了更大的噪声容限,并且其输入阻抗也远大于TTL输入阻抗。

LVCMOS

同TTL一样,鉴于功耗和响应速度的考虑,CMOS也同样衍生出了LVCMOS接口标准,并且由于MOS管相对于三极管的导通门限更加低,因此LVCMOS比LVTTL更容易使用较低的电压进行通信。

常用的LVTTL标准如下:

- LVCMOS3V3

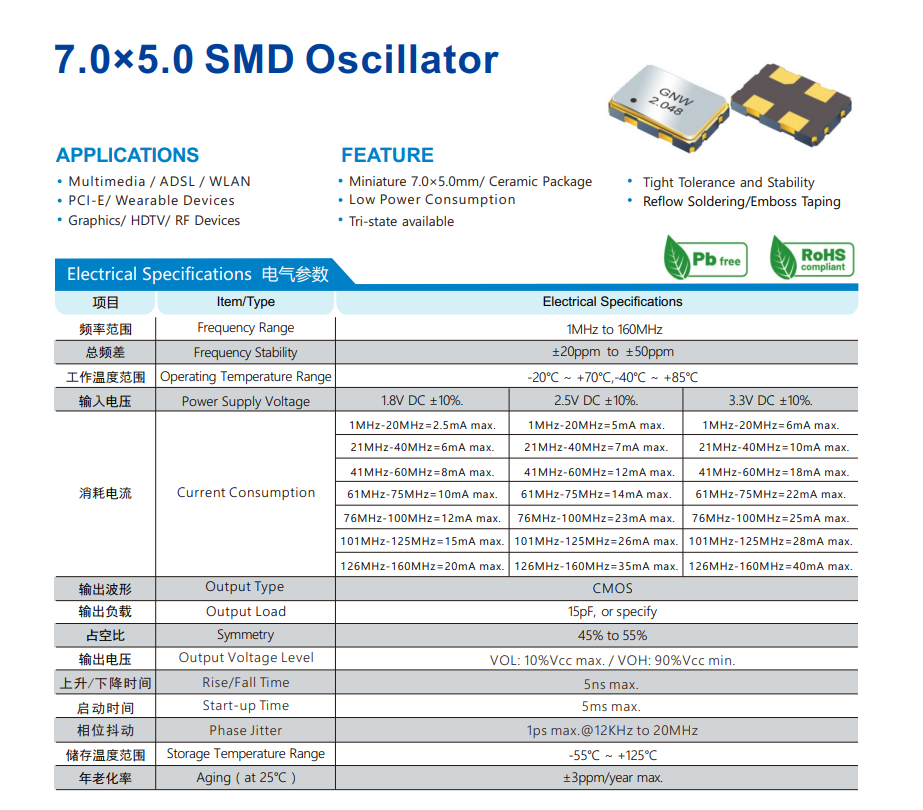

晶诺威科技OSC7050-2.048MHz有源晶振规格参数如下:

LVCMOS3V3,即其内部有源晶振的标准电源供给为3.3V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于3.2V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.7V。

- LVCMOS2V5

LVCMOS2V5,即其内部有源晶振的标准电源供给为2.5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.0V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于1.7V,状态0的判定要求为小于等于0.7V。

- LVCMOS1V8

LVCMOS1V8,即其内部有源晶振的标准电源供给为VCC=1.8V,当然这是有一定容忍度的,不过与之前介绍的电平标准不同,这个容忍度会影响它的输出、输入情况,介绍如下:

对于输出端,状态1的电压要求为大于等于VCC-0.45V (若VCC精确等于1.8V,则为1.35V) ,状态0的电压要求为小于等于0.45V;

对于输入端,状态1的判定要求为大于等于0.65倍的VCC (若VCC精确等于1.8V,则为1.17V) ,状态0的判定要求为小于等于0.35倍的VCC (若VCC精确等于1.8V,则为0.63V) 。

- LVCMOS1V5

LVCMOS1V5,即其内部有源晶振的标准电源供给为VCC=1.5V,它的容忍度也会影响到其输出、输入情况,介绍如下:

对于输出端,LVCMOS1V5没有明确要求,但是肯定是状态1越接近VCC越好,状态0越接近0V越好;

对于输入端,状态1的判定要求为大于等于0.65倍的VCC (若VCC精确等于1.5V,则为0.975V) ,状态0的判定要求为小于等于0.35倍的VCC (若VCC精确等于1.5V,则为0.525V) 。

- LVCMOS1V2

LVCMOS1V2,即其内部有源晶振的标准电源供给为VCC=1.2V,它的容忍度也会影响到其输出、输入情况,介绍如下:

对于输出端,LVCMOS1V2也没有明确的要求,但是肯定是状态1越接近VCC越好,状态0越接近0V越好;

对于输入端,状态1的判定要求为大于等于0.65倍的VCC (若VCC精确等于1.2V,则为0.78V) ,状态0的判定要求为小于等于0.35倍的VCC (若VCC精确等于1.2V,则为0.42V) 。

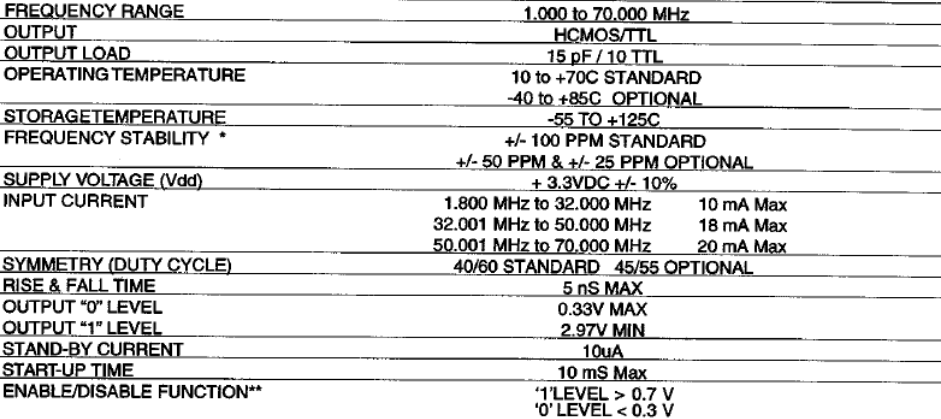

TTL

TTL是Transistor-Transistor Logic的英文缩写,这种接口电平标准的初衷是用于基于三极管结构的数字系统之间的。

工作于TTL接口标准下的数字电路,其内部有源晶振的标准电源供给应为5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.4V,状态0的电压要求为小于等于0.5V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.8V。

也就是需要大于某一个阈值表示电平1,小于某一个阈值表示电平0。

对比输出、输入端的电压要求,可以看出输出端的电压输出要求要比输入端的双阀值判定标准更加严格。这样做主要是考虑到噪声的干扰以及电信号在输出与输入间的传递速度,从而让双阀值判定标准更加的可靠。

LVTTL

由于2.4V与5V之间还有很大空间,这对改善噪声干扰并没有什么明显的好处,而且还会增加系统的功耗;并且由于数字状态1、0之间电平相差较大,还会影响到数字电路的响应速度。因此后来就把TTL的电压范围进行了一些压缩,从而形成了LVTTL(Low Voltage Transistor-Transistor Logic),也即低压TTL电平标准。

目前常用的LVTTL标准有两种,如下。

- LVTTL3V3

LVTTL3V3,即其内部有源晶振的标准电源供给为3.3V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.4V,状态0的电压要求为小于等于0.4V;

对于输入端,状态1的判定要求为大于等于2.0V,状态0的判定要求为小于等于0.8V。

对比输出、输入端的电压要求可知,为了保证双阀值判定的稳定性和抗噪性,输出端的电压要求仍比输入端的双阀值判定标准要严格,这点对于所有的数字系统接口标准是一样的。

- LVTTL2V5

LVTTL2V5,即其内部有源晶振的标准电源供给为2.5V,输出、输入情况如下:

对于输出端,状态1的电压要求为大于等于2.0V,状态0的电压要求为小于等于0.2V;

对于输入端,状态1的判定要求为大于等于1.7V,状态0的判定要求为小于等于0.7V。

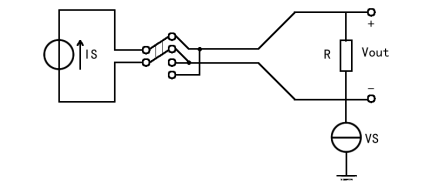

LVDS

LVDS是Low Voltage Differential Signaling的缩写,即低压差分信号,其输入、输出与之前所介绍的接口电平都不同,它需要通过两根线来完成通信。其工作原理如下图所示:

上图左部为LVDS输出端,其内部有一个恒流源IS,大约恒定输出3.5~4mA的电流值。最右边的Vout接入LVDS的输入端,而在靠近输入端的地方并联接入一个阻值为100欧的匹配电阻R。

通过改变上图双刀双掷开关的位置,而改变差分线上电流的方向,以此来表示数字状态0和1,因此,接收端的差分线上将会由于电流方向的不同而表现出来±350mV的差分电平,并依次作为数字状态的判定依据。

上图右侧还有一个直流偏置电压源VS,这主要是用来说明Vout的两端其实一般都是正电压的,实际电路中并没有该项。

由于LVDS的电压摆幅仅有350mV左右,电流也仅有3.5mA左右,而且又是差分传输,因此具有高速、超低功耗、低噪声和低成本等优良特性。

注:

建议为数字系统接口的双方选择一致的标准,如在有源晶振选型时,就需要特别注意晶振规格书中晶振的输出类型。另外,单端和差分是不可能兼容的,因为从物理连线上它们就存在不同。

但是对于同种类的接口,如果A电平标准的输出符合B电平标准的输入,那么就称A的输出可驱动B的输入,如果反之亦然,那么称A、B两种电平标准可相互驱动。例如,CMOS的输出是可以驱动TTL输入的,但是反之则不行,因为TTL的状态1输出仅为大于等于2.4V,并不能达到CMOS判决状态1所需要的大于等于3.5V;但是LVTTL3V3和LVCMOS3V3却可以相互驱动,因为它们的输出都能满足彼此的输入判定要求。

拓展阅读:差分晶振在工业自动化中的作用

关于差分晶振在工业自动化中的作用,晶诺威科技介绍如下:

1、 可编程逻辑控制器PLC

在工业自动控制化生产线中,PLC用于控制各种设备的运行和协同工作。差分晶振提供的高精度时钟信号确保PLC能够精确的执行逻辑控制程序,实现对生产过程的精准控制,提高生产效率和产品质量。

2、 工业以太网设备

随着工业4.0的推进,工业以太网在工业控制领域得到广泛应用,差分晶振为工业以太网交换机、网关等设备提供稳定的时钟信号,保障网络通信的实时性和精准性,确保工业设备之间可靠的数据传输和远程监控。