晶振的一些参数并非固定绝对值,大部分会随工作温度、杂散电容、激励功率等参数的变化而发生变化,在这种情况之下,合格的晶振会保持在正常频率范围内工作,不会造成芯片接收时钟信号的任何异常,但劣质不合格晶振则不同。

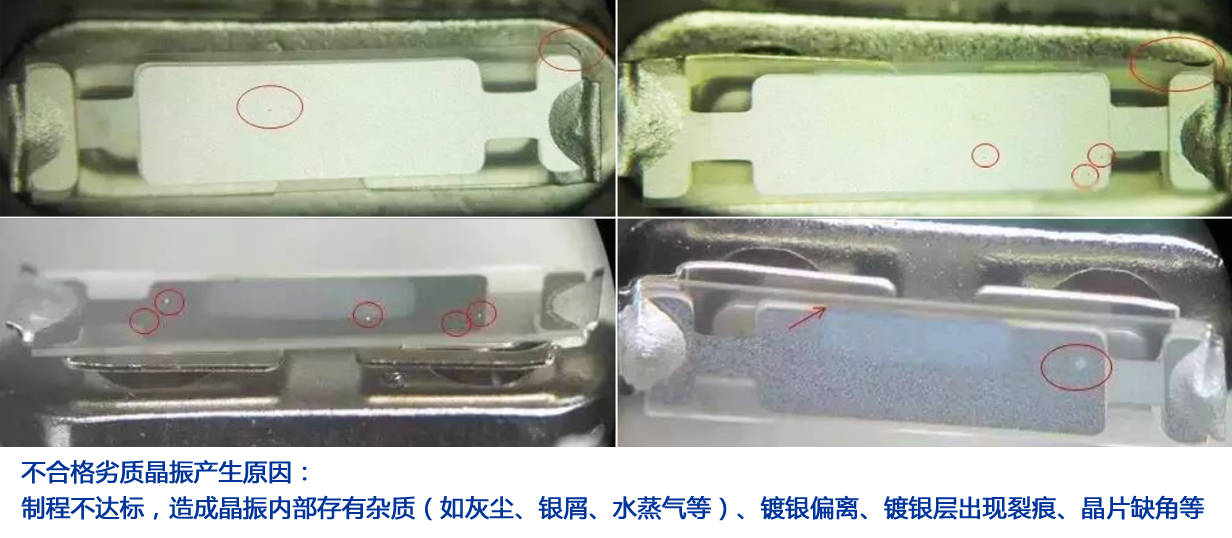

不合格劣质晶振产生原因:制程不达标,造成晶振内部存有杂质(如灰尘、银屑、水蒸气等)、镀银偏离、镀银层出现裂痕、石英晶片缺角等,不良品49S晶振解剖图所示如下(由高倍显微镜拍摄):

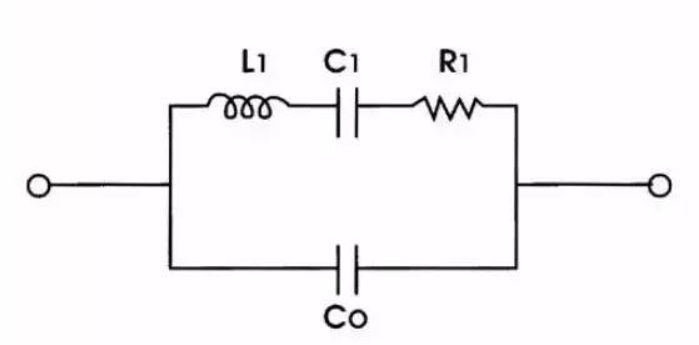

Equivalent Circuit of a Crystal Unit晶振等效电路图如下:

- C0静电容(shunt capacitance):指以石英晶体为介质,由两个电极形成的电容,也称为石英晶体谐振器的并联电容。换句话说,它相当于以石英晶片为介质、以两电极为极板的平板电容器的电容量和支架电容、引线电容的总和。

- R1阻抗(series resistance): 等效石英晶片产生机械形变时材料的能耗

- C1动态电容( motional capacitance):反映其材料的刚性

- L1动态电感(motional inductance):大体反映石英晶片的质量

劣质不合格晶振参数异常主要体现在以下四点:

- DLD2:当不同的功率驱动晶振时,所得之最大阻抗与最小阻抗之差。DLD2越小越好,当晶振制程受污染时,DLD2值会偏高,导致时振与时不振现象。

- RR谐振电阻:越小越好,过大造成晶振起振困难、电路不稳定。合格的晶振设计应在 ESR与C0值之间取得平衡。

- FDLD2:指 不同驱动功率下,F最大与F最小的差值。FDLD2越小越好。FDLD2不良主要原因为制造污染不良,导致时振时不振,造成休眠晶振。

- SPDB: 寄生信号强度与主信号强度比值。SPDB越大越好,如果太小就有可能造成开机时晶振直接频偏,调整外接电容的大小也无法改善。或者过烤机之后(温度变化之后)频偏,冷却或者重启晶振又出现恢复正常工作现象。SPDB <-3dB 为最低要求,以避免晶振输出不需要的副波頻率,导致系统紊乱。