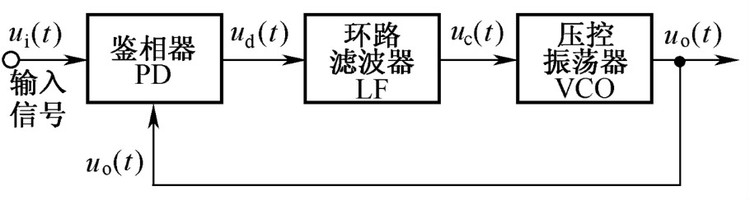

(锁相环PLL倍频原理)

晶振为MCU提供其执行命令时所需的时钟信号,而晶振的标称频率则是用来专门描述这种周期性的输出频率。

晶振标称频率与石英晶片的厚度,面积,切割方式有关,晶片越薄则频率越高。由于生产工艺的限制,晶片不能无限的薄,否则会存在破裂的风险。为了提高晶振的频率,晶振制造中可以采用泛音振荡模式来取代基频振荡模式,但目前泛音晶振及泛音晶振电路已经较少使用。随着晶振研发与制造工艺的发展,晶诺威科技无源贴片晶振可以做到基频振荡模式下标称频率为62.4MHz。

目前,在理想状态下5G网络数据传输速度可达10G/S及以上。如果MCU需要更高更稳定的频率信号,常见的方式是通过锁相环PLL(Phase Locked Loop)将晶振标称频率进行倍频。

锁相环定义

为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。

锁相环一般由以下三部分构成:

- 鉴相器(PD,Phase Detector)

- 环路滤波器(LF,Loop Filter)

- 压控振荡器(VCO,Voltage Controlled Oscillator)

锁相环振荡器(PLL)

锁相环是一种反馈控制系统,它可以将输入信号的相位锁定到晶振产生的输出信号上。

每种振荡器的设计和应用都有其特定的要求,选择合适的驱动方式取决于所需的频率稳定性、功耗、尺寸、成本和应用场合。在设计和应用时,还需考虑晶振的负载、电源电压、温度范围等因素,以确保振荡器的性能满足系统需求。