减少PCB板寄生电容Cp对晶振频率的干扰建议如下:

电容的物理公式:

C=εS/4πKd

说明:

晶振焊盘与邻近地平面之间的面积S和距离d均会影响寄生电容大小,因为面积S不变,所以影响寄生电容的因素只剩下距离d,通过挖空晶振同一层的地和相邻层的地,可以增大晶振焊盘与地平面之间的距离,来达到减小寄生电容的效果。

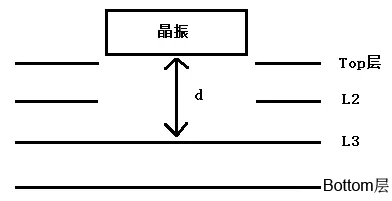

如下图所示,一个4层PCB板,晶振位于Top层,将Top层和相邻层净空之后,晶振相对于地平面(L3),相比较没有净空之前,这个距离d增大,即寄生电容会减小。

晶振的L1和L2层均净空处理

晶振位置需要远离热源,因为高温同样会影响晶振频偏。

晶振附近相邻地挖空处理的目的有两个:

- 维持负载电容恒定

- 隔绝热传导,避免周围的PMIC或者其它发热体的热透过铜皮传导到晶振,导致频偏。晶诺威科技建议净空不铺铜,以隔绝热的传递。