关于晶振电容匹配及晶振电路设计注意事项总结如下:

- 电容匹配—–负载电容是指晶振要正常振荡所需要的电容。一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。要求高的场合还要考虑IC输入端的对地电容。

- 负载电容是指在电路中跨接晶体两端的总的外界有效电容。它是一个测试条件,也是一个使用条件。应用时一般在给出负载电容值附近调整可以得到精确频率。此电容的大小主要影响负载谐振频率和等效负载谐振电阻。

- 一般情况下,增大负载电容会使振荡频率下降,而减小负载电容会使振荡频率升高。

- 负载电容是指晶振的两条引线连接IC块内部及外部所有的有效电容之和,可看作晶振片在电路中串接电容。负载频率不同决定振荡器的振荡频率不同。标称频率相同的晶振,负载电容不一定相同。因为石英晶体振荡器有两个谐振频率,一个是串联揩振晶振的低负载电容晶振:另一个为并联揩振晶振的高负载电容晶振。所以,标称频率相同的晶振互换时还必须要求负载电容一致,不可冒然替换,否则可能会造成电子设备工作不正常。

如果实际的负载电容配置不当,第一会引起线路参考频率的误差。另外,如在发射接收电路上会使晶振的振荡幅度下降(不在峰点),则会直接影响混频信号的信号强度与信噪。

晶振的这两个匹配电容的主要作用是对晶体和振荡电路的补偿和匹配,使电路易于启振并处于合理的激励态下,同时对振荡频率也有一定的“微调”作用。晶振在电流过激励或欠激励的条件之下虽可工作,但前者使晶振容易老化,缩短使用寿命,并导致振荡电路的EMC特性变劣;而后者则可能会导致晶振不易起振,工作稳定性下降。所以电容容量的大小会轻微影响振荡频率的高低、振荡器工作的稳定性、起振的难易程度及温度稳定性等。

附:晶振电路设计注意事项

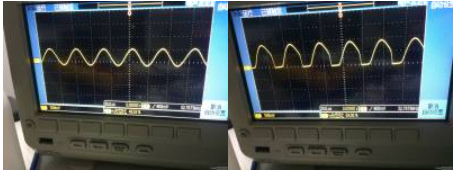

1. 当晶振输出波形出现削峰或畸变时,可增加负载电阻调整(几十K到几百K);若要稳定波形,则可尝试并联一个1M左右的反馈电阻。

2. 使晶振、外部电容器(如果有)与 IC之间的信号线尽可能保持最短。当非常低的电流通过IC晶振振荡器时,如果线路太长,会使它对 EMC、ESD 与串扰产生非常敏感的影响,而且长线路还会给振荡器增加寄生电容。

3. 尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

4. 将晶振外壳接地;当心晶振和地的走线。

拓展阅读:如何有效提升晶振的抗干扰能力可以采取以下措施

在实际应用中,晶振作为频率控制元件,其稳定性和准确性至关重要。然而,晶振容易受到电磁干扰、射频干扰以及电源噪声等外部因素的影响,导致其频率稳定性下降。为了确保晶振的频率稳定性,必须采取有效的抗干扰措施。

晶振受到的干扰主要包括电磁干扰、射频干扰和电源噪声。电磁干扰是由外部电磁场或其他设备产生的辐射或噪声引起的,可能导致晶振工作异常或信号失真。射频干扰主要由无线通信设备、雷达、Wi-Fi路由器、手机等产生的射频信号造成,通过辐射或耦合进入晶振电路,影响其正常的振荡和频率输出。电源噪声是由电源的不稳定性或其他设备的干扰产生的,通过电源线路传导到晶振电路中,影响晶振稳定的频率输出。

为了提升晶振的抗干扰能力,可以采取以下措施:

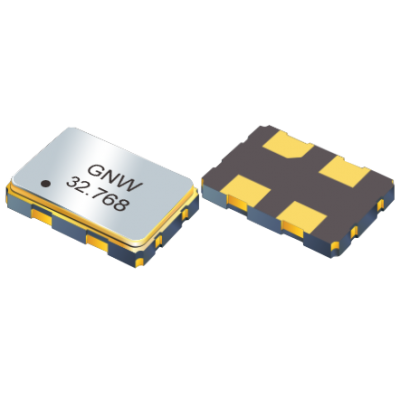

1、选择合适的晶振型号:低相位噪声、低电磁干扰和低射频干扰晶振是提升抗干扰能力的关键。这些晶振型号具有较低的相位噪声和电磁干扰,能够更好地抵抗外部干扰。

2、使用晶体滤波器:晶体滤波器能够有效抑制高频噪声,降低干扰对晶振的影响。通过选择合适的滤波器,可以滤除干扰信号,提高晶振的频率稳定性。

3、采用金属屏蔽外壳:金属屏蔽外壳可以防止电磁辐射进入晶振电路,提高抗干扰性能。通过将晶振封装在金属外壳中,可以减少外部电磁干扰对晶振的影响。

4、优化电路设计:合理的PCB布局能够有效降低干扰耦合,减少外部信号对晶振的影响。尽量减少长引线和高频噪声路径,避免信号反射和干扰。通过优化电路设计,可以降低干扰对晶振的影响,提高其频率稳定性。

5、去耦与稳压:在电源输入端加入去耦电容,以减少电源波动和噪声干扰。同时使用稳压电路,确保晶振获得稳定的电源供给,避免电压波动影响其频率稳定性。通过去耦和稳压措施,可以降低电源噪声对晶振的影响,提高其频率稳定性。

6、应用软件抗干扰技术:通过数字滤波算法进一步降低噪声干扰的影响。对采集到的信号进行数字处理,软件滤波器可以消除外部干扰,提高信号的纯净度和稳定性。通过应用软件抗干扰技术,可以进一步降低干扰对晶振的影响,提高其频率稳定性。

综上所述,晶振的抗干扰技术对于确保其频率稳定性至关重要。通过选择合适的晶振型号、使用晶体滤波器、采用金属屏蔽外壳、优化电路设计、去耦与稳压以及应用软件抗干扰技术,可以有效地抵抗电磁干扰、射频干扰和电源噪声的影响,提高晶振的频率稳定性。