关于时钟信号分频,倍频和锁相环PLL电路相关知识,晶诺威科技整理如下:

锁相环振荡器(PLL):

锁相环是一种反馈控制系统,它可以将输入信号的相位锁定到晶振产生的输出信号上。每种振荡器的设计和应用都有其特定的要求,选择合适的驱动方式取决于所需的频率稳定性、功耗、尺寸、成本和应用场合。在设计和应用时,还需考虑晶振的负载、电源电压、温度范围等因素,以确保振荡器的性能满足系统需求。

- 分频 Divider

指 N分频就是把频率变为1/N。周期变为N倍。

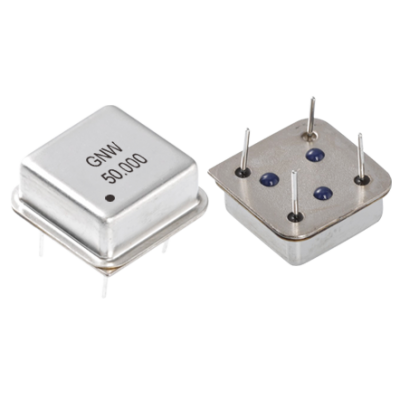

石英晶体加电后产生压电反应,在固定频率振动,产生出电压按照固定周期变化的脉冲信号。高频率信号通向分频器frequency divider,转换为低频信号。

- 倍频 Multiplier

指N倍频就是把频率变为N倍。周期变为1/N倍。

在现代通信中,人们需要更高更稳定的输出频率。尽管LC振荡器可以工作到较高的频率,但是稳定度不高,而晶体振荡器有较高的稳定度和准确度,只是基频较低。在现代无线通信中,频率合成技术(例如锁相技术PLL)可以从低频的晶体振荡器中获得高稳定的高频信号。

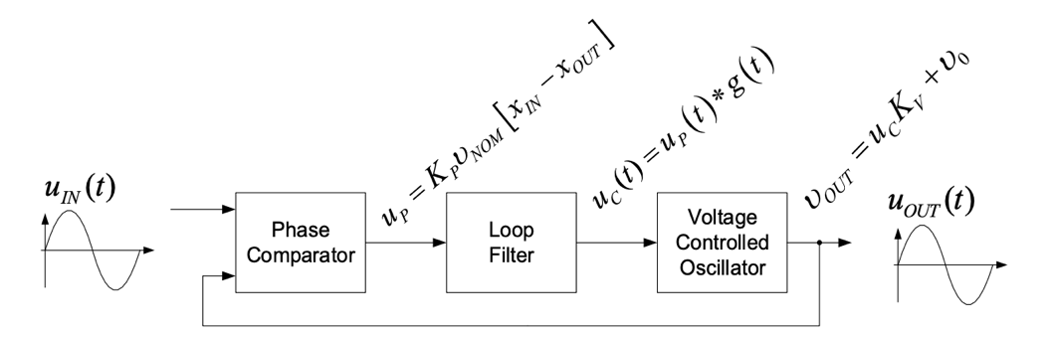

- 锁相环PLL电路

指锁相环电路是闭环的反馈控制系统。PLL由以下几部分组成:

1、Phase Comparator鉴相器/相位比较器:对输入的基准信号和反馈回路的信号进行频率比较。

2、Loop Filter回路滤波器:由分频器实现,将VCO的输出降低到和基准信号相同的级别频率。

3、VCO压控振荡器:根据输入电压,输出对应频率的周期信号。

4、Feedback Loop反馈回路