若VCXO额定输入电压为5V,当实际输入电压为2.5V时,晶振输出频率为中心频率。

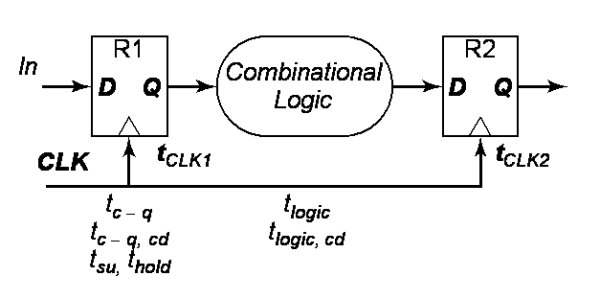

电源的表现形式也可看做为波形的一种。当占空比为0时,实质为直流电。在VCXO实际工作中,由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异。相位不可能与参考源完全吻合,这个时候就会出现时钟倾斜(Clock skew)现象。由此可见,Skew指的就是时钟相位上的不确定。

Skew=Tclk1-Tclk2

通常,我们会通过调整VCXO的电压高低来给鉴相器指令信号,把相位与参考源在时间轴上同步(即,调整两者的跟随度到一致)。调整动作完成后,再通过锁相环PLL加以锁定。

时钟偏差/倾斜Clock Skew的程度大小会对设备性能造成负面影响,一般设计中都需要专门留取10%左右的margin,以备后期调整。

注:

VCXO调整的不是晶振频率精度,而是在晶振精度基础上,调整相位在时间轴上的前后,使之与参考源尽可能同步。否则,即使晶振精度已经达到IC要求,若时钟偏差/倾斜Clock Skew过大,造成晶振PPM值(如±10PPM)整体偏移,也会造成设备通讯不稳定。