(晶振输出波形:方波和正弦波)

关于振荡器,最常见的问题是:单端输出和差分输出之间有什么区别,它们最适合哪些应用?

根据应用和所需工作频率,有几种输出类型可供选择。以下是一些更详细的不同输出,以更好地了解每个输出的优点和缺点。这应该可以让您更好地了解哪种类型最适合您的应用程序。

振荡器主要的输出格式主要有两种:正弦波(Sine Wave)和方波(Square Wave)

正弦波

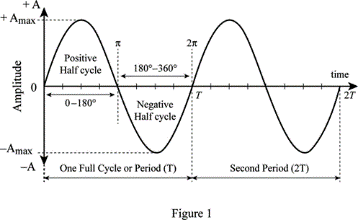

如下图所示,产生连续的模拟正弦波,该正弦波以频率和振幅的速率表示扫描周期。

方波

如下图所示,是振荡器输出的数字表示。它的信号以频率和幅度的速率表示为90度周期。

关于输出类型:单端输出与差分输出

单端输出

![]() Sine Wave and Clipped Sine Wave

Sine Wave and Clipped Sine Wave

![]() TTL (Transistor to Transistor Logic) 0.4 ~ 2.4V

TTL (Transistor to Transistor Logic) 0.4 ~ 2.4V

![]() CMOS (Complementary Metal Oxide Semiconductor) 0.5 ~ 4.5V

CMOS (Complementary Metal Oxide Semiconductor) 0.5 ~ 4.5V

![]() HCMOS (High Speed CMOS) 0.5 ~ 4.5V

HCMOS (High Speed CMOS) 0.5 ~ 4.5V

![]() LVCMOS (Low Voltage CMOS) 0.5 ~ 4.5V

LVCMOS (Low Voltage CMOS) 0.5 ~ 4.5V

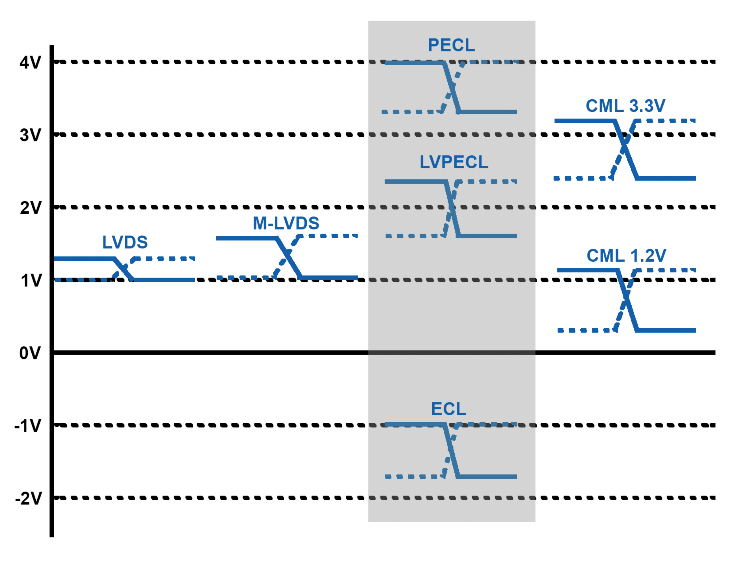

差分输出

![]() PECL (Positive Emitter Coupled Logic) 3.3 ~ 4.0V

PECL (Positive Emitter Coupled Logic) 3.3 ~ 4.0V

![]() LVPECL (Low Voltage PECL) 1.7 ~ 2.4V

LVPECL (Low Voltage PECL) 1.7 ~ 2.4V

![]() CML (Current-Mode Logic) 0.4 ~ 1.2V and 2.6 ~ 3.3V

CML (Current-Mode Logic) 0.4 ~ 1.2V and 2.6 ~ 3.3V

![]() LVDS (Low Voltage Differential Signaling) 1.0 ~ 1.4V

LVDS (Low Voltage Differential Signaling) 1.0 ~ 1.4V

![]() HCSL (High Speed Current Steering Logic) 0.0 ~ 0.75V

HCSL (High Speed Current Steering Logic) 0.0 ~ 0.75V

哪种振荡器输出信号类型最适合您的应用?

让我们来看看每种方法的优点和缺点。首先来看单端输出模式:

正弦波和削峰正弦波

正弦波

正弦波是晶体或振荡器电路的标准或“自然”信号输出。它由一个基本正弦频率输出组成。理想的振荡器能保持频率长时间稳定,无频率变化,输出波形为清晰的正弦波输出。线性正弦波输出提供所有输出中最佳的相位噪声性能。正弦波非常适合需要高质量输出信号的应用。

削峰正弦波

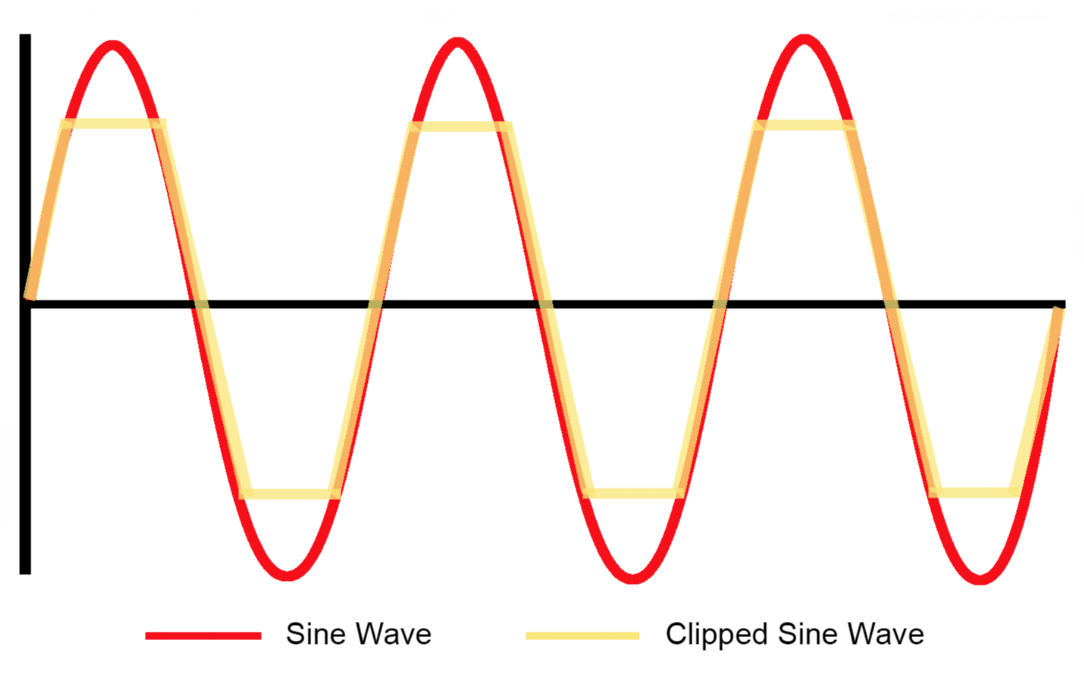

正弦波输出被抑制,因此它不会达到其最大高点或最低点。通过这样做,您可以在不牺牲任何所需相位噪声性能的情况下创建方波输出。在下图中,您会看到红色的正弦波和黄色的削峰正弦波。

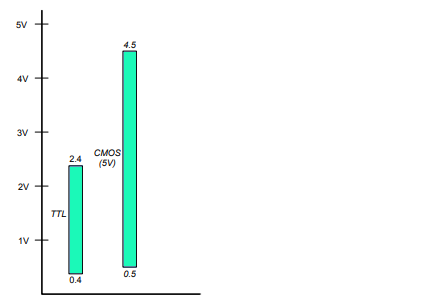

CMOS, HCMOS and LVCMOS

CMOS, HCMOS and LVCMOS是最适合较低频率时钟(通常低于250 MHz)的方波数字输出。这允许在时钟输出和芯片输入之间建立直接连接。在大多数情况下,可以使用低值串联电阻来有效减少信号反馈并保持可靠的信号完整性。还有高速和低电压选项,可能更适合您的特定需求。

TTL or Transistor to Transistor Logic

这是一种较旧的数字输出标准,并且大部分已被CMOS技术所取代。这是因为CMOS提供了更低的成本和更好的噪声性能。CMOS和TTL都非常适合低功耗,更高的输出摆幅和相对较低的成本。

差分输出信号的选择

差分输出提供 180° 异相的双输出信号线。这对信号质量有很多好处,包括:

![]() 更好的上升和下降时间

更好的上升和下降时间

![]() 卓越的抖动和相位噪声性能

卓越的抖动和相位噪声性能

![]() 得到优化的共模噪声抑制

得到优化的共模噪声抑制

![]() 有助于减少电磁和射频干扰

有助于减少电磁和射频干扰

ECL or Emitter Coupled Logic

ECL主要是作为TTL的良好替代品而引入的。ECL电路可以非常快速地改变状态,这使其更适合高速数据传输。差分输出的缺点之一是它们需要更高的电源电流才能工作。ECL在使用过程中也使用负电源。在尝试连接到正基电源设备时,这可能会带来挑战。

PECL and LVPECL

PECL输出经常用于高速时钟分配电路。这是因为PECL具有高抗噪性,能够在长线路长度上驱动高数据速率,并且由于电压摆幅较大而具有良好的抖动性能。但是,PECL需要高功耗才能运行,这是主要缺点。

LVPECL 为千兆以太网和光纤通道的使用提供了良好的基础。LVPECL在电气上与LVDS类似,但提供较大的差分电压摆幅和略低的功率效率。LVPECL的输出可能会带来挑战,因为需要端接才能发出电压。此外,芯片中的差分电路可能具有不同的输入容差。请务必检查是否正确终止以获得最佳性能。

Current-Mode Logic (CML)

CML具有与LVPECL相似的性能。这里的主要区别在于CML不需要外部偏差。这使得CML成为低功耗时低压PECL的良好替代品。

Low Voltage Differential Signaling (LVDS)

LVDS类似于低压输出,但LVDS的功耗较低,并且电压摆幅较小。LVDS通常用于高速数据传输需求,如时钟分配或背板收发器。对于更高的数据速率,通常首选HCSL、CML或LVPECL,但需要比LVDS更多的功耗。其他优点包括降低对噪声的敏感性,并且易于在CMOS IC中实现。

High Speed Current Steering Logic (HCSL)

HCSL有一个更新的输出标准,就像LVPECL一样。HCSL的一个优点是其高阻抗输出和快速开关时间。建议使用10至30 Ω串联电阻,以减少可能的过冲。其他优点包括最快的开关速度、低功耗(介于LVDS和LVPECL之间)以及平均到良好的相位噪声性能。

总结:

1、为了便于使用: LVDS输出只需要接收器上的单个电阻,而LVPECL则需要在发射器和接收器两端接。

2、对于更高频率: LVDS、LVPECL和HCSL具有比CMOS更快的转换速度,但需要更多功耗。

3、为了降低功耗:如果频率高于150 MHz,我们建议使用CMOS或LVDS 。

4、为了获得最佳抖动性能:建议选择顺序为 LVPECL、 LVDS,然后是CMOS(如果你的频率足够低的话)。