如何调整晶振电路的负性阻抗Negative Resistance Value?解释如下:

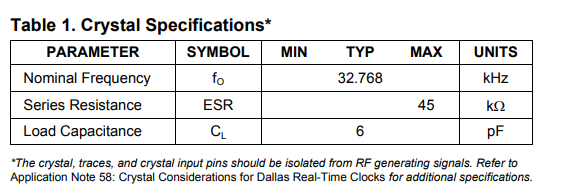

一般而言,负性阻抗值应满足不少于晶振标称最大阻抗(ESR/Equivalent Series Resistance/等效串联电阻)的3-5倍。如:若32.768KHz晶振ESR=45KΩ,则建议负性阻抗Negative Resistance Value在200kΩ以上。由此可见,在无源晶振起振电路中,负性阻抗的大小直接决定着晶振的起振能力。

- 如果负性阻抗(余量)过大,可以尝试通过将晶振外接电容C1和C2的值调大来降低负性阻抗。

- 如果负性阻抗(余量)太小,可以尝试选择较小ESR的晶振或将晶振外接电容C1和C2的值调小来实现增大负性阻抗的目的。

注:

- 如果无源晶振不起振,我们不建议通过提高其额定激励功率(Drive Level)来解决该问题,原因是过高激励功率会造成晶振过驱,导致晶振频率不稳定或损坏。一般32.768KHz晶振激励功率为0.1μW~0.2μW。

- 如果无源晶振不挂外接电容,可能造成晶振频率输出不稳定。