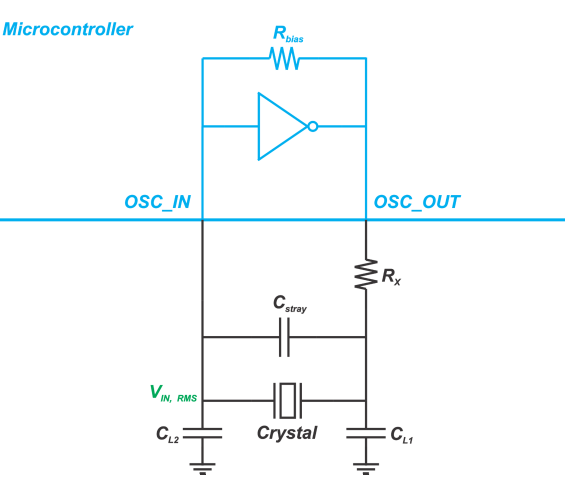

在晶振起振电路中的Cstray指的是什么电容?

Cstray,简称Cs,指的是晶振引脚至芯片管脚的走线电容(即杂散电容总和,包括电路走线、晶振引脚及芯片引脚的所有寄生电容)。一般Cstray的典型值取3~5pF或4~6pF之间。

因为电路板走线设计或复杂程度不同,杂散电容存在不同差异。需要指出的是,如果电路板中的杂散电容过多,会直接影响晶振起振电路中的负载电容总量的变化,其结果是导致晶振工作不稳定,包括起振慢或频率偏差过大。由此可见,在晶振的起振电路中,其Cstray(杂散电容)越小越好。总之,过多的Cstray(杂散电容)是造成无源晶振振荡电路最不稳定的原因之一。

注:

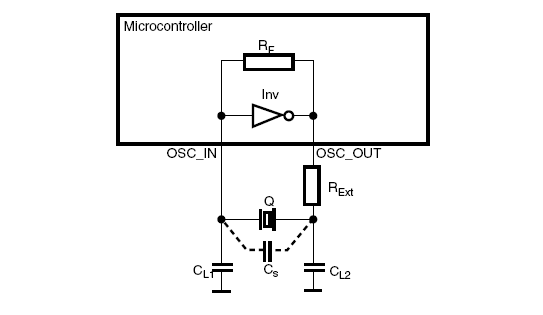

- CL1和CL2为无源晶振的外部匹配电容(需要通过计算得出)。

- Cstray为电路、晶振引脚 及芯片引脚的寄生电容总和(一般通过估算得出,如3~5pF)

- CL则为我们需要的晶振参数—负载电容(晶振电气参数之一,在晶振手册中可找到)。

拓展阅读:晶振的杂散电容:概念、影响与调整方法

在电子系统中,晶振是一种常用的频率标准元件,其精度和稳定性对整个系统的性能有着至关重要的影响。然而,晶振的实际使用中,其频率并不是完全准确的,常常会存在一定的偏差。这种偏差除了来自于温度变化、电压变化、机械应力和制造偏差等因素外,还有一个重要的来源就是晶振的杂散电容。

一、晶振的杂散电容

1.杂散电容的定义

晶振的杂散电容是指存在于电路板各处,不经意间形成的电容。这些电容通常是由于导线和元器件之间的绝缘不完全或者元件之间的间距过小导致的。杂散电容的存在使得晶振的输出频率精度及稳定性受到影响。

2.杂散电容的影响

杂散电容对晶振的性能产生负面影响。首先,杂散电容会改变晶振的负载,从而影响其频率输出。其次,杂散电容的存在会导致电路中的能量损失增加,使得晶振的稳定性和可靠性降低。此外,杂散电容还可能引起电路中的谐波干扰,进一步影响系统的性能。

二、控制晶振杂散电容的方法

1.选择合适的电路板材料

电路板材料对晶振的性能有着重要影响。选择具有低介电常数的材料作为电路板材料,可以降低杂散电容的影响。此外,提高电路板的绝缘性能也可以有效减少杂散电容的产生。

2.优化电路板布局和走线

在电路板布局和走线时,需要考虑到晶振的位置和连接方式。合理布局和走线可以减小晶振与其他元件之间的耦合电容,从而降低杂散电容的影响。此外,对于高频信号线,需要尽量减小其长度和弯曲程度,以减少信号失真和干扰。

3.增加去耦电容

在晶振附近增加去耦电容可以有效地减小电源和地线上的噪声,从而降低杂散电容的影响。去耦电容的选择需要根据具体的电路情况进行确定。

4.提高元件的装配精度

提高元件的装配精度可以减小元件之间的距离和偏差,从而降低杂散电容的产生。此外,采用具有高稳定性的元件也可以提高整个系统的性能。

晶振的杂散电容是影响其性能的一个重要因素。为了减小杂散电容的影响,需要从电路板材料选择、电路板布局和走线、增加去耦电容以及提高元件装配精度等方面进行控制。通过采取这些措施,可以有效地提高晶振的精度和稳定性,从而提升整个电子系统的性能。