若晶振输出频偏为正,外接匹配电容是减小还是增大?

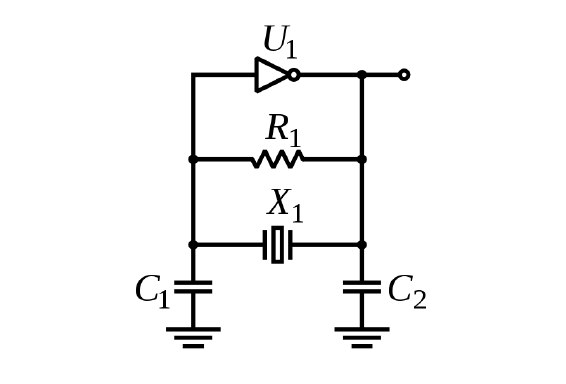

答:若实测无源晶振输出频率为正(偏快)的话,建议适当增加外接电容值。规律:外接电容增大,频率下降;外接电容减小,频率上升。

举例:如果原来外接电容为22PF,建议先增加至27PF,然后上电测试结果。

一般情况下,外接电容(单个)调整范围在:6PF~33PF之间。针对两颗电容C1和C2,建议等值调整。

拓展阅读:

晶振受哪些外界因素影响会出现频偏?

1、晶振的工作受温度影响,不同的温度下晶振的频率会有所变化。温度变化时,原子间距会发生变化,导致晶振的谐振频率也会发生变化。

2、电源波动会导致晶振的工作电压发生变化,从而影响晶振的频率。

3、当晶振的负载阻抗发生变化时,会影响晶振的频率。

4、如果晶振安装位置不正确或受到震动,可能会导致其谐振频率发生变化。

如何最大化程度地减少晶振频偏的影响?

1、选择温度系数较低的晶振,可以减小温度变化对晶振频率的影响。

2、确保电源电压稳定,避免过高或过低的电压影响晶振的频率。

3、根据实际应用情况,选择合适的负载阻抗,确保晶振能够正常工作。

4、将晶振安装在正确的位置,确保其不受震动的影响。同时,在安装时可以采取一些措施来减小应力对晶振的影响,如使用橡胶垫等。

5、对于需要高精度时钟信号的应用,可以定期对晶振进行校准,以确保其频率的准确性。

其它注意事项

1、在选择晶振时,需要了解其性能参数,如频率范围、温度系数、负载电容等,以确保其能够满足实际应用的需求。

2、在安装和使用晶振时,需要注意其电气性能,如阻抗、相位噪声等,以确保其能够正常工作并满足系统的要求。

3、晶振容易受到其它高频元件的干扰,因此需要采取一些措施来减小干扰的影响,如使用屏蔽线、滤波器等。

4、对于一些重要的时钟信号,需要采取一些保护措施,如使用稳压器、滤波器等,以减小电源波动和负载变化对晶振的影响。