(电路板上电测试12MHz晶振频偏+61ppm)

为什么需要测试晶振是否频偏超差?

答:如果晶振在实际工作中的输出频率偏差太大,可能超出时钟芯片对其的捕捉范围,造成指令错误,引发系统紊乱。因此在样机阶段,上电测试并验证晶振实际输出的频率精度是否合格尤为关键。

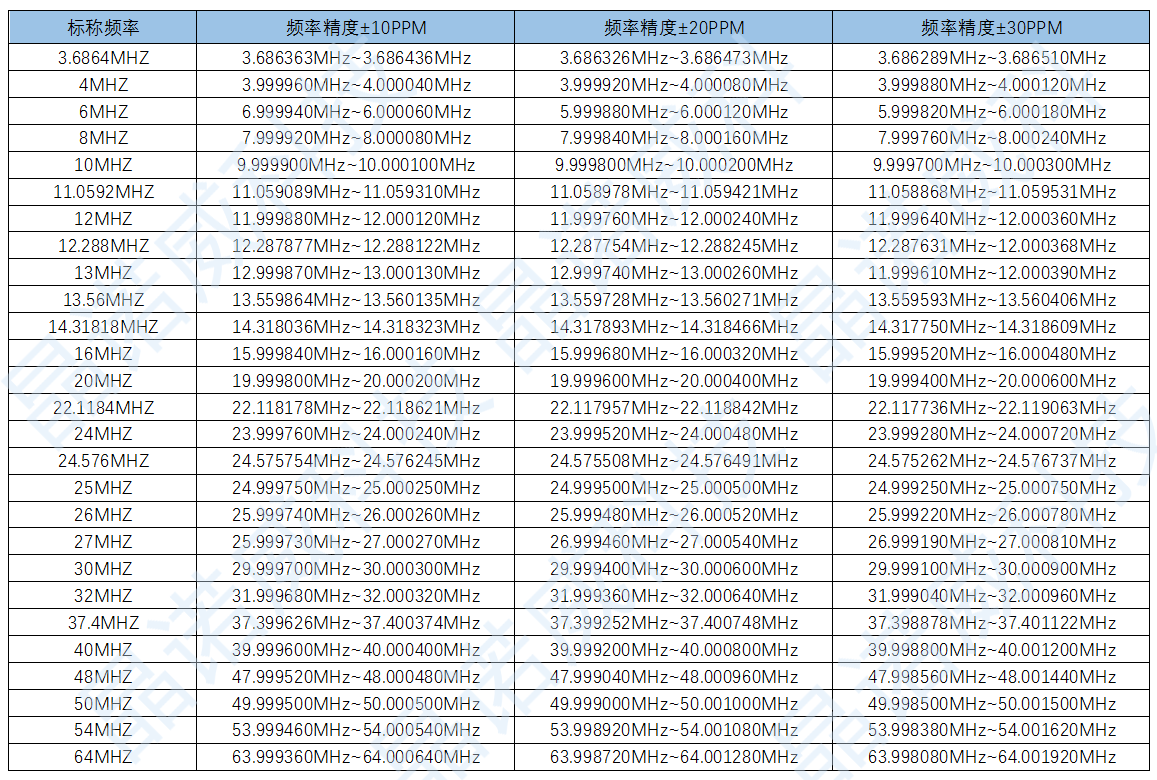

晶诺威科技产常见晶振频率精度对照表如下:

晶振输出频率偏差过大的影响

![]() 设备性能下降:

设备性能下降:

当晶振频率偏差过大,会导致系统时钟信号的准确性和稳定性受到影响,进而影响整个设备的性能。例如,在智能手机或平板电脑上,晶振偏差可能导致应用程序的反应时间变慢,影响用户体验。

![]() 电路模块故障:

电路模块故障:

晶振频率偏差可能导致某些电路模块无法正常工作。例如,某些无线通信模块对时钟信号的精度要求极高,晶振偏差可能会影响通信质量甚至导致模块故障。

![]() 系统稳定性降低:

系统稳定性降低:

频率偏差可能导致系统的不稳定,增加死机或重启的可能性。在长期使用中,这将严重影响设备的寿命。

![]() 辐射干扰增加:

辐射干扰增加:

晶振频率偏差可能引发电磁辐射的增加,对其他电子设备造成干扰,甚至可能违反相关电磁干扰和电磁兼容性标准。

关于晶振频偏应对策略

![]() 定期校准:

定期校准:

对于使用中的晶振,定期进行校准是降低频率偏差的有效方法。一般而言,生产厂家会提供相应的校准服务,以确保产品的性能稳定。

![]() 选择合适的晶振:

选择合适的晶振:

在选择晶振时,应考虑其频率稳定性、温度特性等关键指标,尽量选择与系统要求匹配的型号。

![]() 硬件调整:

硬件调整:

对于某些特定应用,可以通过调整晶振的安装位置、周围元件等,来改善其性能。但这通常需要一定的专业知识和经验,不建议普通用户自行操作。

![]() 软件补偿:

软件补偿:

对于一些可以通过软件进行补偿的设备,可以通过编写相应的算法,对晶振的输出频率进行实时监测和调整,以减小频率偏差对系统的影响。

![]() 故障预警:

故障预警:

为确保设备在晶振出现故障时能及时发现,可以设置一些简单的预警机制。如频率监测器等,当频率偏差超过一定阈值时,发出警告信息。