关于有源晶振电气参数“占空比”,晶诺威科技解释如下:

英文:Symmetry / Duty Cycle

中文:占空比

晶振占空比定义

指晶振在一个周期内的高电平和低电平所占的比例。

关于晶振占空比,晶诺威科技详解如下:

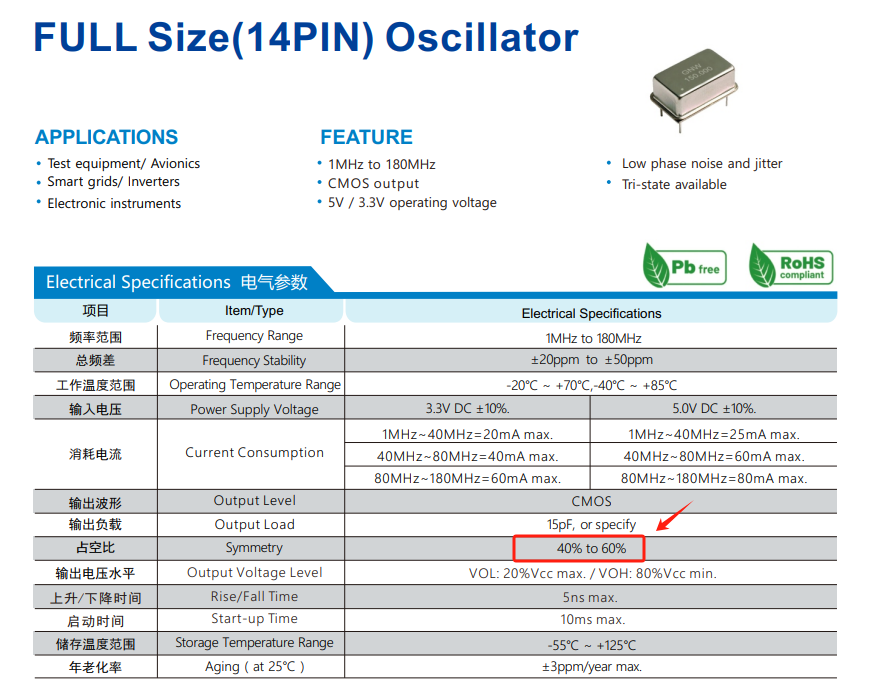

(Symmetry/Duty Cycle for PXO dip-14)

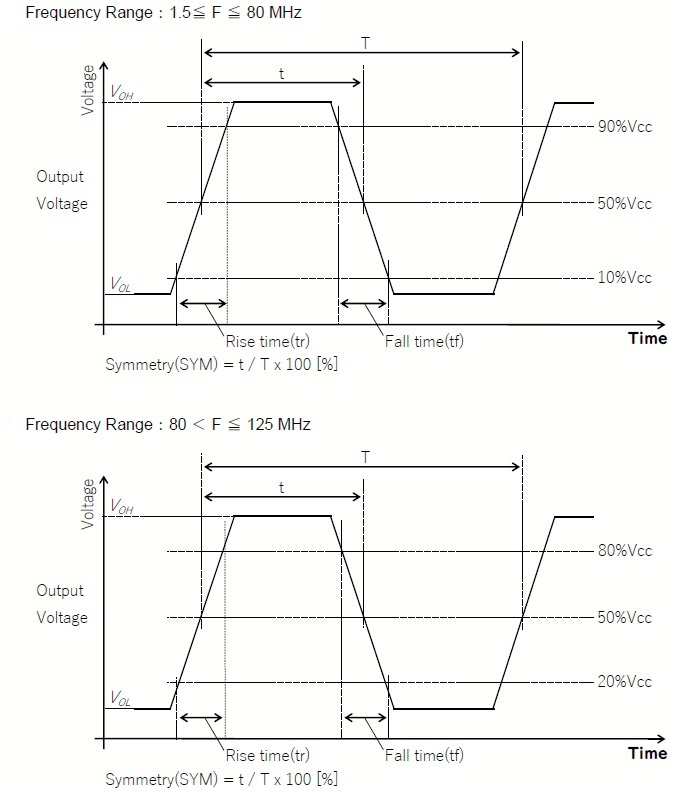

晶振占空比是衡量晶振性能的重要指标之一,对于数字电路的稳定性和可靠性具有重要影响。晶振占空比的计算公式为:占空比=高电平时间/一个周期的时间。其中,高电平时间是指晶振输出的高电平持续时间,一个周期的时间是指晶振输出一个完整周期所需要的时间。

晶振占空比的大小与晶振的工作频率有关。在数字电路中,晶振的工作频率一般为固定值,例如10MHz、20MHz等。在这种情况下,晶振占空比的大小只取决于高电平时间和一个周期的时间。晶振占空比的大小对于数字电路的稳定性具有重要影响。占空比过大或过小都会导致数字电路的工作不稳定。过大的占空比会导致电平不稳定,可能引起信号误判,影响系统的正常工作;过小的占空比则会导致信号幅度过小,可能引起信号丢失,导致系统无法正常工作。

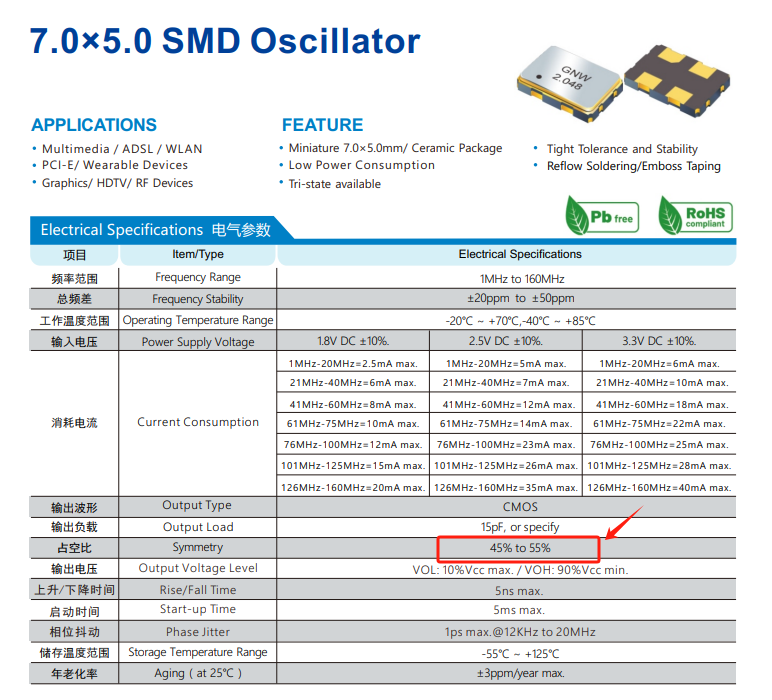

(晶诺威科技产有源晶振OSC7050占空比:45%~55%)

为了保证数字电路的稳定性,晶振占空比的设计需要符合一定的要求。一般来说,晶振占空比应尽量接近50%(如40%~60%或45%~55%)。这是因为在占空比为50%时,晶振输出的高电平时间和低电平时间相等,电平稳定性最好。当然,在实际设计中,由于各种因素的影响,无法完全达到50%的占空比。因此,在设计中通常会在晶振的输出端加上适当的滤波电路,以调整晶振占空比,使其接近50%。

注:

无源晶振/晶体谐振器输出波形为正弦波,因此占空比默认为50%。