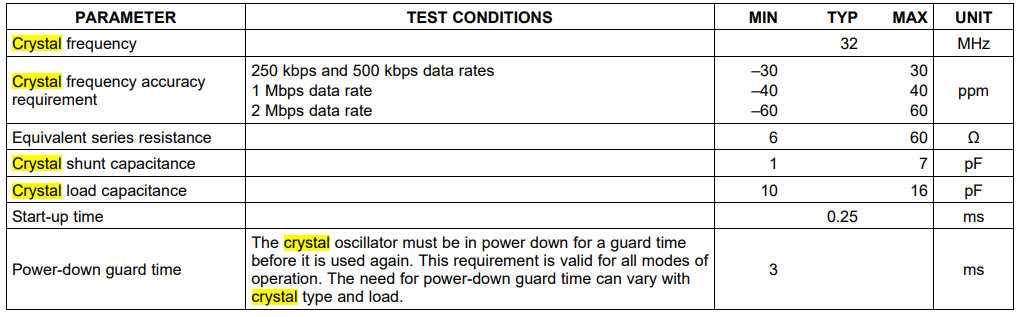

晶振负载电容CL=20PF,两端分别接多大电容?

答:建议27PF~33PF。

以上外接电容匹配参数仅为参考,晶诺威科技建议以电路板上电后晶振实测输出频率精度为准。

外接电容值调整原则如下:

![]() 若实测晶振频率偏正向,如晶振12MHz,实测频率为12.000840,尝试往下微调外接电容值。

若实测晶振频率偏正向,如晶振12MHz,实测频率为12.000840,尝试往下微调外接电容值。

![]() 若实测晶振频率偏负,如晶振12MHz,实测频率为11.999060,尝试往上微调外接电容值。

若实测晶振频率偏负,如晶振12MHz,实测频率为11.999060,尝试往上微调外接电容值。

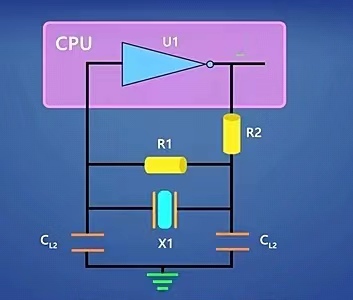

晶振的工作原理主要基于石英晶体的压电效应。晶振在特定的频率下产生振动,产生稳定的时钟信号,其被广泛应用于各种电子设备中。

当时钟系统失去准确的节拍,会导致整个系统的运行混乱,最终影响芯片的工作。具体来说,晶振失效可能会导致芯片无法正常工作,出现时序错乱、数据传输错误、误判等故障,严重时甚至可能导致芯片无法启动。一些高端芯片对时钟精度和稳定性要求非常高,如果晶振失效,不仅会导致芯片不稳定,还会影响芯片的运算精度和功耗性能,最终导致芯片的性能下降。此外,还可能加速芯片的老化,进而导致芯片寿命缩短。