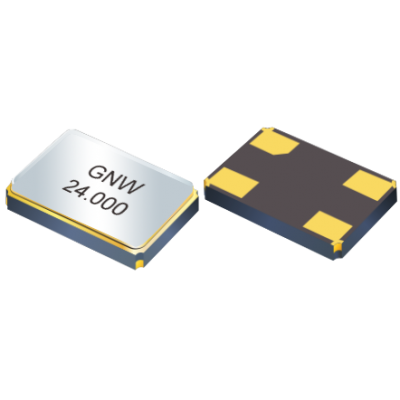

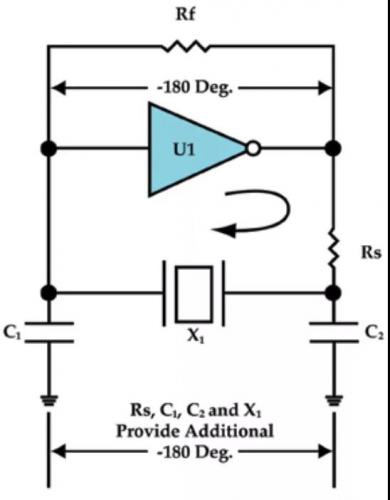

要想理清这一点,需要首先了解晶振的工作原理,及对芯片的作用。我们都知道,晶振是被动电子元器件,只有在足够电激励条件下,内置石英晶片才会发生机械振动,基本步骤如下:

1、晶振受到足够激励功率发生固有频率的机械振动。

2、在该机械振动所产生的机械力(压力或拉力)作用下,石英晶片的两端会产生电荷,并形成电流。

3、该电流会反馈给电路。

4、电路把接收到的该反馈进行信号放大。

5、电路利用该放大后的电信号来再次激励晶振进行机械振动。

6、晶振再将自身晶片振动产生的电流反馈给电路,如此循环。

7、当电路中的激励电信号和晶振标称频率相同时,电路就会输出信号强大、频率稳定的正弦波。

8、整形电路再将正弦波变成方波送到数字电路中供IC使用。

基于晶振的输出能力很微弱,它仅仅能够输出以毫瓦为单位的电能量。在 IC(集成电路) 内部,需要通过放大器将这个信号放大几百倍甚至上千倍才能满足电路的正常需求。晶振和 IC之间通常以一段导线或数段导线连接,根据电磁感应原理,导线在垂直方向切割磁力线时会产生电流,因此导线越长,产生的电流越强。

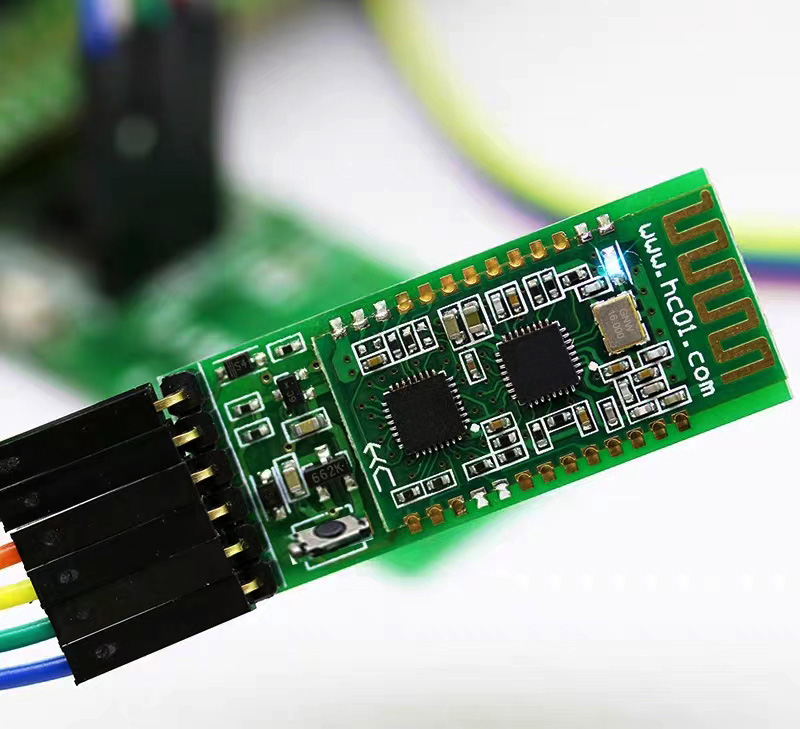

现实中,其实磁力线并不常见,但电磁波却像幽灵一样无处不存,它是一种看不见摸不着的能量载体:例如:基站、蓝牙设备、无线网络、手机通讯等。晶振和IC之间的连线到达一定长度就变成了接收天线,连线越长,接收的信号就越强,产生的电能量就越强,然而一旦它接收到的电信号强度接近或超过晶振产生的信号强度时,因受到干扰,IC内的放大电路输出的将不再是固定频率的方波,而是无比杂乱的信号,这导致数字电路无法同步工作而功能性瘫痪。

由此可见,在设计PCB布线时,晶振到芯片的距离需要尽量缩短。为了避免系统中最严重的电磁干扰(EMI:Electromagnetic Interference),晶振必须尽量靠近所属IC。

总之,将晶振放在IC附近是出于对信号稳定性、传输延迟、抗干扰能力、电源管理、布局优化和兼容性等多方面的考虑。这种布局设计有助于确保电子设备能够高效、稳定地运行,提高系统的性能和可靠性,并确保数字电路能够正常工作。

了解更多晶振相关资讯,请点击晶诺威官网以下链接:

- 如何减少辐射对时钟信号的干扰?

- 如何降低电磁对晶振时钟信号的干扰

- 晶振频率受干扰的不良现象和解决方案

- PCB晶振布线抗干扰(EMI)设计介绍

- 为何说提供时钟信号的晶振是数字电路的心脏?

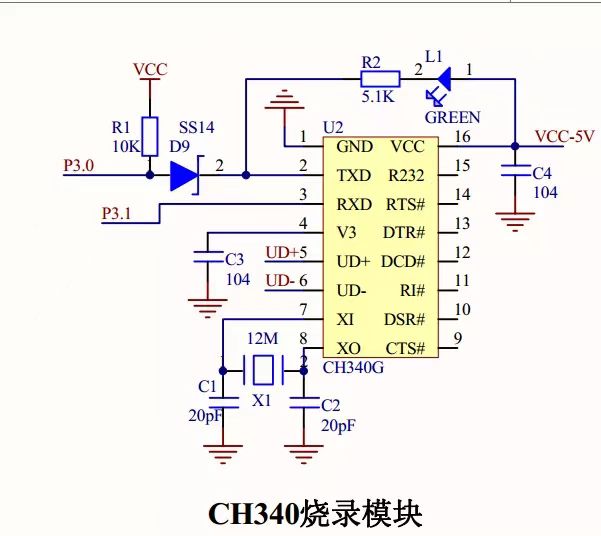

- PCB设计中晶振时钟信号电路介绍

- 晶振PCB正确布线需要哪些注意事项?

- 从软件角度看晶振的作用及MCU工作流程

- EMC测试项目及电磁波对晶振的影响

- 晶振位于线路板边缘会带来哪些隐患?

- 晶振受电磁干扰的解决方案

- 如何选择高品质晶振生产厂家?

- 晶振振荡电路中负性阻抗到底是什么?

- 你对晶振的激励功率了解有多少?

- 晶振的激励功率怎么设定

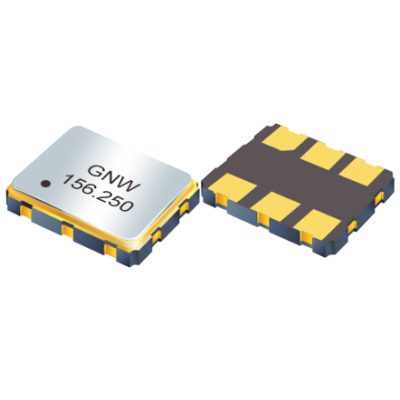

- 有源晶振的输出波形分类和应用介绍

- 晶振输出波形和电路形式介绍

- 有源晶振电路设计:如何降低噪音

- 振荡电路的工作原理介绍