关于展频晶振抗干扰与时钟精度的冲突问题,晶诺威科技分析如下:

Every electronic product designer has to deal with the issue of electromagnetic compatibility (EMC) or electromagnetic interference (EMI) on a daily basis – especially when using frequency-determining components such as quartz oscillators. The ICs installed into quartz oscillators generate steep, sharp-edged flanks and produce strong harmonic overtones. Spread-spectrum oscillators are one solution to this, but there are many applications where they are not to be selected. With a center spread of ±0.5 %, for example, the output frequency is modulated within a range of ±0.5 %. Given a frequency of 33.333 or 66.666 MHz, a frequency modulation of ±0.5 % would imply a frequency modulation range of 33.333 MHz ±166.665 kHz or 66.666 MHz ±333.330 kHz – too great for precise clocking. These applications typically only allow ±50 ppm. A frequency stability of ±50 ppm equates to a tolerance of ±1.66665 kHz at 33.333 MHz, or a tolerance of ±3.3333 kHz at 66.666 MHz. In such cases, the developer has so far had to take very expensive measures to reduce EMC – EMI.

针对每个电子产品,设计师每天都要面对电磁兼容性(EMC)或电磁干扰(EMI)的问题——尤其是在使用频控器件石英振荡器时。在集成电路中,石英振荡器内部的IC可能会导致其产生我们不期望的各种谐波。展频振荡器是解决这一问题的一种方法,但在许多应用中不能使用展频振荡器。例如,当中心频率扩展为±0.5%时,输出频率在±0.5%的范围内调制。给定33.333MHz或66.666 MHz的频率,±0.5%的频率调制意味着33.333 MHz晶振频率调制范围为±166.665 kHz或66.666MHz晶振频率调制范围为±333.330kHz。这对于高精度时钟需求的设备来说意味着频偏太大了,因为一些应用通常只允许时钟偏差在±50ppm以内。±50ppm频率稳定度等于在33.333 MHz时的容差为±1.66665 kHz,或在66.666 MHz时的容差为±3.3333 kHz。在这种情况下,研发者不得不采取非常昂贵的措施来减少EMC-EMI。

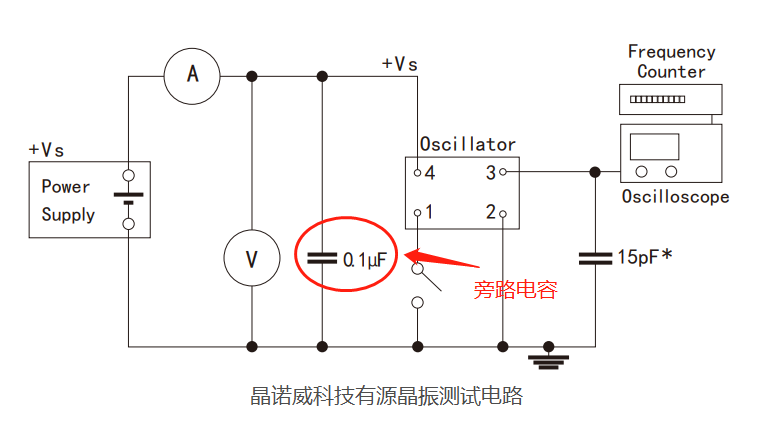

In the clock oscillator circuit design, the specialists of Genuway Technology recommend using a 0.1 μF decoupling capacitor between the supply voltage and ground pins. This considerably minimizes the influences of the supply voltage.

在时钟振荡器电路设计中,晶诺威科技建议在电源电压和接地引脚之间使用0.1μF去耦电容,以大大减少来自电源电压的影响。

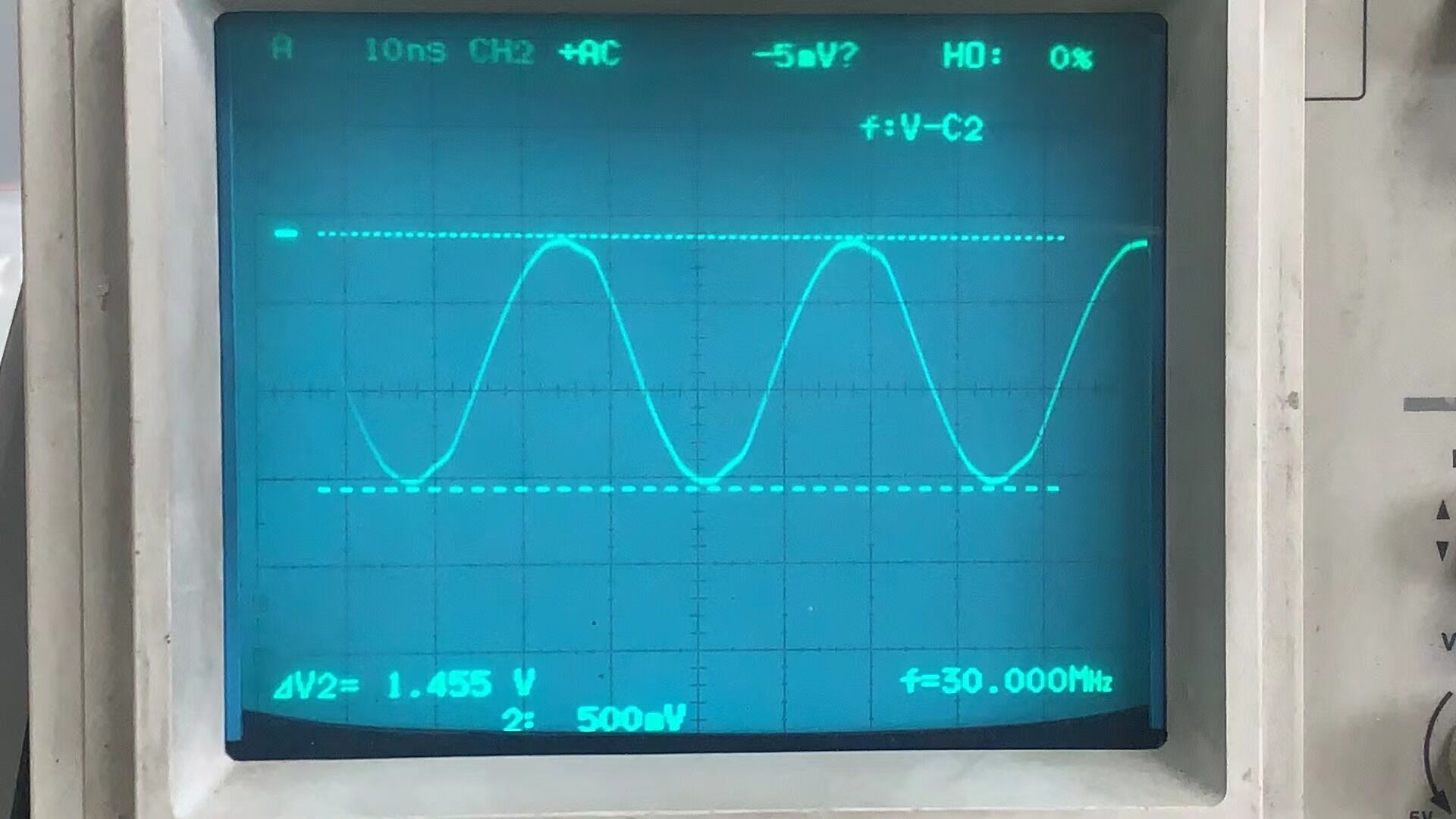

It is also a good try to use the sine wave output oscillators made by Genuway to reduce the unnecessary harmonic overtones.

采用晶诺威科技生产的正弦波输出晶体振荡器来减少不必要的谐波也是一种不错的尝试,如下图所示: