关于晶振周边电路及晶振匹配电路常见问题,晶诺威科技分析如下:

如果晶振经过验证被确认为良品,那么确实需要进一步排查晶振周围的电路以及与电路的匹配问题。以下是详细的排查步骤:

1、检查线路连接

使用万用表:使用万用表的“响铃”功能或电阻档来检查晶振与周围电路的连接是否存在虚焊或短路。虚焊点可能表现为高电阻值或不稳定的连接,而短路则可能显示为非常低的电阻值或零欧姆。

目视检查:仔细观察晶振引脚与电路板之间的焊接情况,确保引脚焊接牢固,没有冷焊、断裂或错位。

2.、确认负载电容和负载电阻

查阅规格书:根据所使用的单片机或芯片的规格书,确保选用了正确的负载电容和负载电阻值。规格书中通常会详细说明推荐的负载电容范围和值。

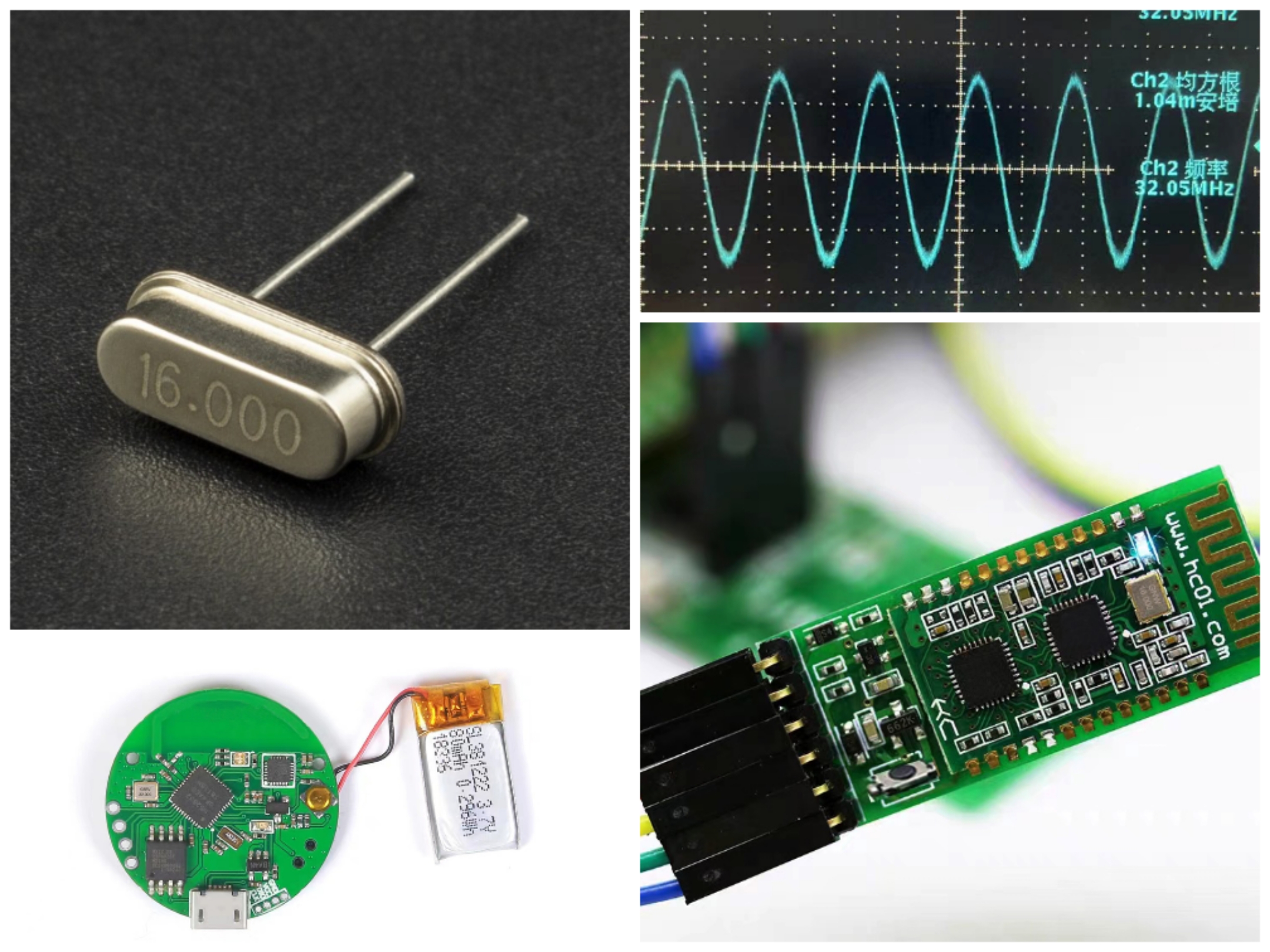

使用示波器:通过示波器观察晶振两端的波形,可以帮助判断负载电容是否匹配。如果波形不稳定或振幅过小,可能是负载电容值不正确。

3、 PCB Layout 分析

检查布局:使用电路设计软件或手动检查PCB Layout,确保晶振电路与单片机或芯片引脚的布局尽可能靠近,以减少信号传输的干扰和损耗。

接地和电源分布:确保晶振附近的接地和电源分布合理,没有电源或地线过孔导致的信号干扰。

4、 软件程序配置检查

时钟系统配置:查看软件程序中关于时钟系统的配置,确保晶振引脚被正确配置为振荡器功能,而不是被错误地配置为普通IO。

晶振频率设置:确认软件中晶振频率的设置与实际使用的晶振频率一致。如果频率设置错误,可能会导致系统工作不正常。

5、其它可能性因素

电源稳定性:检查电源供应是否稳定,因为电源波动也可能影响晶振的起振。

温度影响:在某些情况下,晶振可能受到温度的影响。确保晶振工作在推荐的温度范围内。

电磁干扰:检查周围是否有强电磁干扰源,如高频设备或强磁场,这些都可能影响晶振的工作。