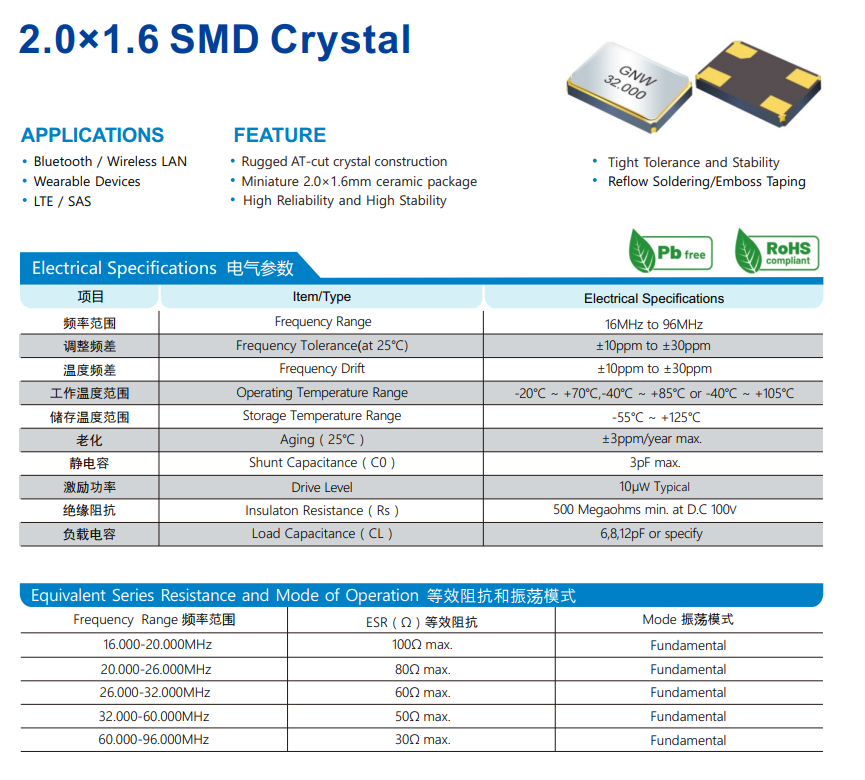

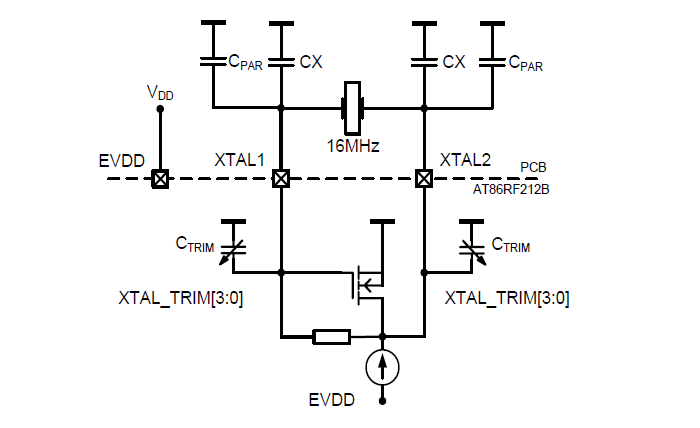

(16MHz无源晶振电路)

关于负载电容(CL)对晶振电路的影响,晶诺威科技解释如下:

Generally, crystals with a higher load capacitance are less sensitive to parasitic pulling effects caused by external component variations or by variations of board and circuit parasitic. On the other hand, a larger crystal load capacitance results in a longer start-up time and a higher steady state current consumption.

一般来说,具有较高负载电容的晶体(无源晶振/晶体谐振器)对由外部元件变化或电路板和电路寄生变化引起的寄生牵引效应不太敏感。从另一方面来看,晶体负载电容越大,其启动时间越长,稳态下电流消耗越大。