关于晶振电路抗扰性及优化方案,晶诺威科技解释如下:

电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。

1、电源噪声

电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运行,进一步加剧失效。

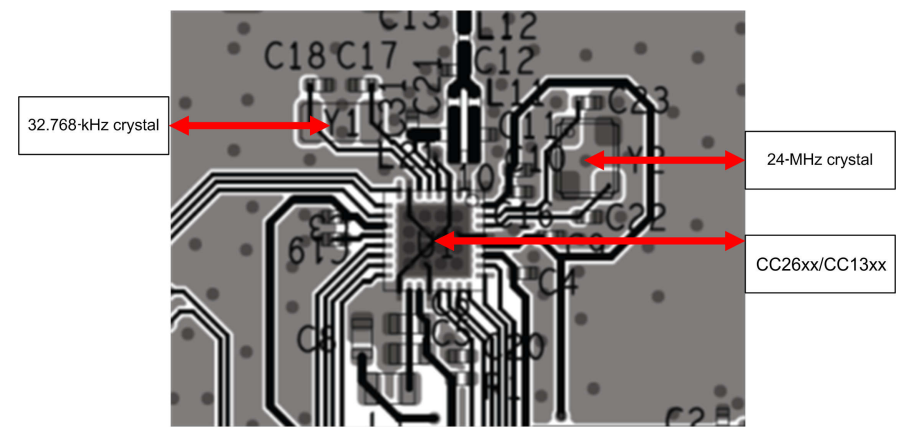

2、电磁干扰

电磁干扰是另一个常见的电路抗扰性问题。电子设备中存在的高频信号源可能引起电磁干扰,从而使晶振的工作受到干扰。

提高电路的抗扰性是解决晶振失效问题的关键,晶诺威科技建议措施如下:

1、加强电源线路的过滤和综合保护,降低电源噪声。可以尝试使用滤波电容、稳压电路等设备来减小电源噪声。

2、设计良好的地线和电源线路布局,降低电磁干扰。可以尝试采用屏蔽罩、隔离层等措施来避免电磁干扰。

3、断开与晶振相关的其他干扰源,如远离高频信号源、电磁辐射源等。