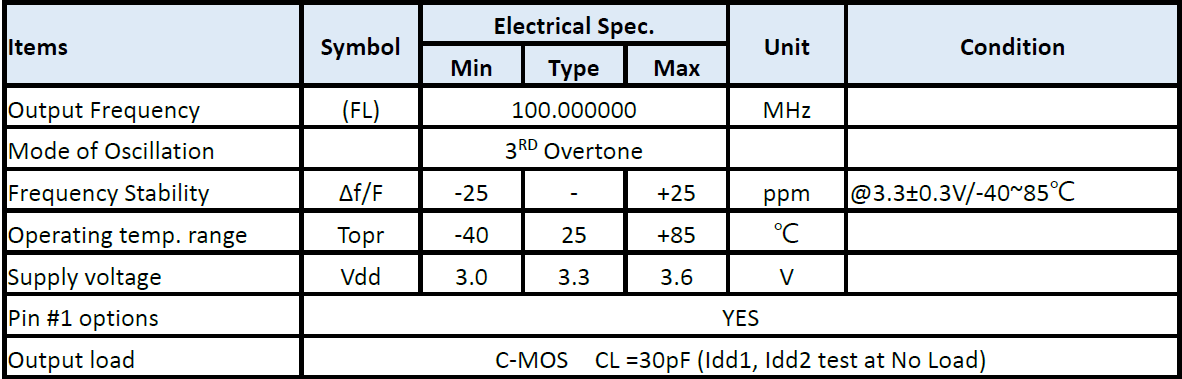

(OUTPUT FREQUENCY=100MHz;OUTPUT LOAD=30pF)

一个有源晶振可以供两个芯片使用吗?

答:是的,一般情况下一个有源晶振可以为两个芯片提供时钟信号,但需注意以下事项:

1、 信号完整性(Signal Integrity)

阻抗匹配:确保晶振输出阻抗与传输线匹配,避免信号反射。

布线长度:尽量缩短晶振到两个芯片的布线,减少信号衰减和延迟。

2、 负载能力(Output Load)

驱动能力:确认晶振的输出驱动能力足以支持两个芯片的负载。通常情况下,有源晶振的输出负载为15pF。如果无法满足,可以选择驱动能力更强的有源晶振,如输出负载(OUTPUT LOAD)=30pF或50pF。如下表所示:

有源晶振2.048MHz,输出负载:50pF

| tems | Electrical Spec. | Unit | Notes | ||

| Min. | Type. | Max. | |||

| 1. Nominal Frequency (FL) | 2.048 | MHz | |||

| 2. Output Waveform | HCMOS Square wave(方波) or TTL 兼容 | ||||

| 3. Frequency tolerance | -10 | +10 | ppm | @ 25℃±3℃ | |

| 4. Supply voltage | 4.5 | 5.0 | 5.5 | V | Vdd |

| 5. Frequency stability | -20 | +20 | ppm | @-40℃~+85℃ | |

| 6. Operable temperature range | -40 | +85 | ℃ | ||

| 7. Output load | 50 | pF | |||

| 8. Output Voltage High | 90% Vdd |

V | VoH | ||

| 9. Output Voltage Low | 10% Vdd |

V | VoL | ||

| 10. Symmetry | 45 | 50 | 55 | % | |

| 11. Current consumption | 10 | mA | |||

| 12. Rise & Fall time | 5 | ns | |||

| 13. Start-up time | 5 | ms | |||

| 14. Enable Voltage High | 70% Vdd |

V | Vhi | ||

| 15. Disable Voltage Low | 30% Vdd |

V | Vlo | ||

| 16. Storage temperature range | -40 | +85 | ℃ | ||

| 17. Aging | -3 | +3 | ppm/Year | 1st Year at 25℃ | |

3、 电源噪声(Power Supply Noise)

电源滤波:建议在晶振电源引脚附近添加去耦电容,减少电源噪声干扰。

地线设计:确保地线低阻抗,避免地弹噪声影响信号。

4、 布局布线(Layout)

对称布线:尽量使晶振到两个芯片的布线对称,减少信号延迟差异。

远离干扰源:避免晶振和时钟信号线靠近高频或高噪声电路。

5、 芯片同步(Chip Clock Synchronization)

同步要求:如果两个芯片需要严格同步,需确保时钟信号相位一致。