-

; ) 为何外接电容越大晶振起振越慢?

2021-08-18首先说明的是:但凡需要外接电容的晶振均为无源晶振。另外,注意区分外接电容C1和C2(接地电容,对地电容)并不等同于晶振负载电容(CL)。C1和C2是电路板和包括IC 和晶振在内的组件的总电容值。 一般情况下,增大无源晶振的外接电容将会使晶振振荡频率下降,即偏负向。举例,若无源晶振12MHz的外接电容…

为何外接电容越大晶振起振越慢?

2021-08-18首先说明的是:但凡需要外接电容的晶振均为无源晶振。另外,注意区分外接电容C1和C2(接地电容,对地电容)并不等同于晶振负载电容(CL)。C1和C2是电路板和包括IC 和晶振在内的组件的总电容值。 一般情况下,增大无源晶振的外接电容将会使晶振振荡频率下降,即偏负向。举例,若无源晶振12MHz的外接电容… -

; ) 如何设计无源晶振及两颗外接电容在PCB的最佳位置?

2021-08-17无源晶振及两颗外接电容在PCB的位置 两颗外接电容应尽量靠近晶振引脚(频率输入脚与频率输出脚)设计。 晶振核心部件为石英晶体,容易受外力撞击或跌落影响而破碎。在PCB布线时最好不要把晶振设计在PCB边缘,尽量使其靠近芯片。 晶振走线需要用GND保护稳妥,远离敏感信号源,如RF及高速信号,以免频率信号…

如何设计无源晶振及两颗外接电容在PCB的最佳位置?

2021-08-17无源晶振及两颗外接电容在PCB的位置 两颗外接电容应尽量靠近晶振引脚(频率输入脚与频率输出脚)设计。 晶振核心部件为石英晶体,容易受外力撞击或跌落影响而破碎。在PCB布线时最好不要把晶振设计在PCB边缘,尽量使其靠近芯片。 晶振走线需要用GND保护稳妥,远离敏感信号源,如RF及高速信号,以免频率信号… -

; ) 晶振周围相噪phase noise源及相噪对策

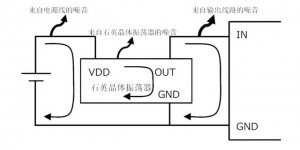

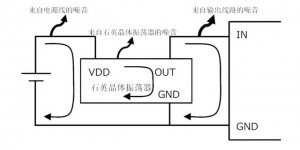

2021-08-13(石英晶体振荡器周围可产生相噪的电路) 相噪phase noise发生源分为主要三大类: (1)来自电源线的相噪:在晶振工作过程中,电源线中将产生脉动。电源线起到天线的作用脉动作为相噪释放。防止电源相噪时重要的是如何阻止或吸收晶振所产生的脉动流入电源线。为此而采取的对策可防止其它元器件所产生的外來相…

晶振周围相噪phase noise源及相噪对策

2021-08-13(石英晶体振荡器周围可产生相噪的电路) 相噪phase noise发生源分为主要三大类: (1)来自电源线的相噪:在晶振工作过程中,电源线中将产生脉动。电源线起到天线的作用脉动作为相噪释放。防止电源相噪时重要的是如何阻止或吸收晶振所产生的脉动流入电源线。为此而采取的对策可防止其它元器件所产生的外來相… -

; ) 如何控制晶振时钟信号的偏移skew?

2021-08-13晶振时钟信号偏移skew概念 整个芯片中时钟信号到达各级电路的时间差即为时钟偏移skew。 造成晶振时钟信号偏移skew的根本原因 短路径问题:即逻辑单元速度快,输出数据比时钟传播到下个逻辑单元还要快,就会造成数据丢失,从而导致逻辑功能出错。 如何控制晶振时钟信号的偏移skew?建议有以下五点: 添…

如何控制晶振时钟信号的偏移skew?

2021-08-13晶振时钟信号偏移skew概念 整个芯片中时钟信号到达各级电路的时间差即为时钟偏移skew。 造成晶振时钟信号偏移skew的根本原因 短路径问题:即逻辑单元速度快,输出数据比时钟传播到下个逻辑单元还要快,就会造成数据丢失,从而导致逻辑功能出错。 如何控制晶振时钟信号的偏移skew?建议有以下五点: 添… -

; ) 晶振低相噪low phase noise电路设计图

2021-08-12晶振低相噪low phase noise电路主要包括以下四个方面: 旁路电容器: 旁路电容器常用于除去相噪(noise)。它可以降低交流电源的阻抗使电路稳定工作,还可以吸电源线中的相噪。大多相噪问题可通过选择安装适宜常数的旁路电容器來解决。 旁路电容器容量: 通常使用的旁路电容器容量大致在0.01u…

晶振低相噪low phase noise电路设计图

2021-08-12晶振低相噪low phase noise电路主要包括以下四个方面: 旁路电容器: 旁路电容器常用于除去相噪(noise)。它可以降低交流电源的阻抗使电路稳定工作,还可以吸电源线中的相噪。大多相噪问题可通过选择安装适宜常数的旁路电容器來解决。 旁路电容器容量: 通常使用的旁路电容器容量大致在0.01u… -

; ) 关于有源晶振频率偏差问题的解决方案

2021-08-12一般情况下,若选对所需精度的有源晶振,在实际工作中,有源晶振发生频偏问题很少见。 现归纳导致有源晶振频率偏差的主要因素如下: 1、 环境温度超出有源晶振规定工作温度范围。 解决方案:更换晶振,选择宽温有源晶振,如:把工作温度-20℃~+70℃改为-40℃~+85℃晶振产品。 2、电源变化可能导致有源…

关于有源晶振频率偏差问题的解决方案

2021-08-12一般情况下,若选对所需精度的有源晶振,在实际工作中,有源晶振发生频偏问题很少见。 现归纳导致有源晶振频率偏差的主要因素如下: 1、 环境温度超出有源晶振规定工作温度范围。 解决方案:更换晶振,选择宽温有源晶振,如:把工作温度-20℃~+70℃改为-40℃~+85℃晶振产品。 2、电源变化可能导致有源… -

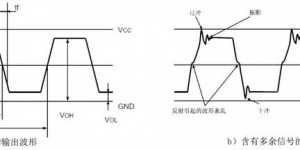

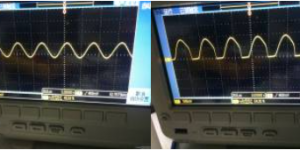

; ) 为何测试无源晶振频率输出脚与频率输入脚频率或波形不一样

2021-08-12(32.768KHz无源晶振频率输出脚与频率输入脚实测频率或波形不一样范例) 如上图所示,测试无源晶振频率输出脚与频率输入脚频率或波形不一样,属于正常现象,因为一个是经由放大器的输出,振幅比较大。另外一个是放大器的输入,信号由输出端经晶振过来,振幅减弱,比较小。另外,测试仪表的探针电容大小、频宽差异…

为何测试无源晶振频率输出脚与频率输入脚频率或波形不一样

2021-08-12(32.768KHz无源晶振频率输出脚与频率输入脚实测频率或波形不一样范例) 如上图所示,测试无源晶振频率输出脚与频率输入脚频率或波形不一样,属于正常现象,因为一个是经由放大器的输出,振幅比较大。另外一个是放大器的输入,信号由输出端经晶振过来,振幅减弱,比较小。另外,测试仪表的探针电容大小、频宽差异… -

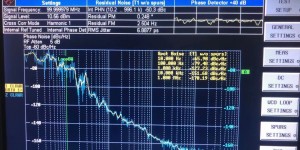

; ) 不同晶振及晶振电路产生的相位噪声phase noise原因及分析

2021-08-09关于不同晶振及晶振电路产生的相位噪声phase noise原因,晶诺威科技分析如下: 在低噪声晶振设计中,电路是非常重要的环节,振荡电路应该要使晶振的有载Q值不致下降很多,并且电路附加的噪声要足够小。 有源晶振常见的类型为普通晶振XO,温补晶振TCXO,恒温晶振OCXO,他们之间直观的不同,就是频率…

不同晶振及晶振电路产生的相位噪声phase noise原因及分析

2021-08-09关于不同晶振及晶振电路产生的相位噪声phase noise原因,晶诺威科技分析如下: 在低噪声晶振设计中,电路是非常重要的环节,振荡电路应该要使晶振的有载Q值不致下降很多,并且电路附加的噪声要足够小。 有源晶振常见的类型为普通晶振XO,温补晶振TCXO,恒温晶振OCXO,他们之间直观的不同,就是频率… -

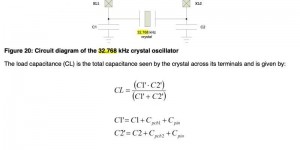

; ) RTC晶振SMD3215(FC-135)32.768KHz电路图

2021-08-07晶振32.768KHz专用于实现系统的RTC实时时钟功能,因此又被广泛称之为表晶。目前最常见封装类型为SMD3215,与爱普生生产的FC-135为替代关系。 SMD3215 32.768KHz主要参数如下: 尺寸:3.2MM*1.5MM 负载电容(CL):12.5PF、9PF、7PF、6PF 频率精…

RTC晶振SMD3215(FC-135)32.768KHz电路图

2021-08-07晶振32.768KHz专用于实现系统的RTC实时时钟功能,因此又被广泛称之为表晶。目前最常见封装类型为SMD3215,与爱普生生产的FC-135为替代关系。 SMD3215 32.768KHz主要参数如下: 尺寸:3.2MM*1.5MM 负载电容(CL):12.5PF、9PF、7PF、6PF 频率精… -

; ) 减少晶振周边电路相噪phase noise的两项最重要方法

2021-08-06晶振周围电路的合适设计对减少相噪noise极为重要。只要电路设计妥善适宜,即可很大程度避免相噪问题,从而充分发挥电子元器件本身所具有的性能。 减少晶振周边电路相噪的方法主要有以下两点: 缩短输岀线路 输出线路是电路中最容易释放相噪的部分。为此,在设计电路图案之际,应当最优先设计输岀线路部分,采用长度…

减少晶振周边电路相噪phase noise的两项最重要方法

2021-08-06晶振周围电路的合适设计对减少相噪noise极为重要。只要电路设计妥善适宜,即可很大程度避免相噪问题,从而充分发挥电子元器件本身所具有的性能。 减少晶振周边电路相噪的方法主要有以下两点: 缩短输岀线路 输出线路是电路中最容易释放相噪的部分。为此,在设计电路图案之际,应当最优先设计输岀线路部分,采用长度…