-

; ) 如何通过串联电阻降低晶振相噪phase noise,避免输出波形output waveform失真?

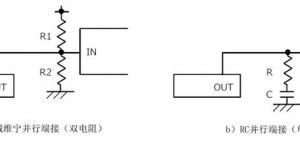

2021-08-05串联电阻降低晶振相噪(phase noise)避免输出波形(output waveform)失真方法介绍 主要分为连接串联电阻与连接终端电阻两部分: 连接串联电阻: 晶振连接输入对象的元器件时,通常产生过冲、下冲或振铃等波形变形。这些变形的波形中含有振荡频率的约3-7倍的射频成份,将引发相噪,所以必…

如何通过串联电阻降低晶振相噪phase noise,避免输出波形output waveform失真?

2021-08-05串联电阻降低晶振相噪(phase noise)避免输出波形(output waveform)失真方法介绍 主要分为连接串联电阻与连接终端电阻两部分: 连接串联电阻: 晶振连接输入对象的元器件时,通常产生过冲、下冲或振铃等波形变形。这些变形的波形中含有振荡频率的约3-7倍的射频成份,将引发相噪,所以必… -

; ) 如何避免晶振输岀波形output waveform失真?

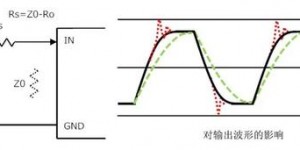

2021-08-04避免晶振输岀波形output waveform失真的关键是需要稳定的输岀线路,确保输入侧所需tr、tf、VOH、VOL等波形特性,即:应当去除不必要的信号,例如过冲、下冲、振影或反射波等。而且,还应降低输岀线路的作为天线释放相噪的效率,使相噪难以释放。 如下图所示:

如何避免晶振输岀波形output waveform失真?

2021-08-04避免晶振输岀波形output waveform失真的关键是需要稳定的输岀线路,确保输入侧所需tr、tf、VOH、VOL等波形特性,即:应当去除不必要的信号,例如过冲、下冲、振影或反射波等。而且,还应降低输岀线路的作为天线释放相噪的效率,使相噪难以释放。 如下图所示: -

; ) Electrical Specifications for SMD3215-2PIN 32.768KHz

2021-07-22Electrical Specifications of SMD3215-2PIN 32.768KHz Features Reflow resistance type crystal units Higher frequency pull ability and lower equivalent s…

Electrical Specifications for SMD3215-2PIN 32.768KHz

2021-07-22Electrical Specifications of SMD3215-2PIN 32.768KHz Features Reflow resistance type crystal units Higher frequency pull ability and lower equivalent s… -

; ) 为什么高温焊接可能会造成石英晶振不良?

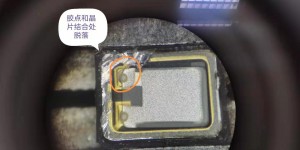

2021-07-21在石英晶片的两个对应面背银作为电极,由电极焊接引线至管脚,气密性封装外壳(真空并充氮气),这样就制造出石英晶体谐振器,简称石英晶振或晶振。 若晶振高温焊接方法不当,会直接造成晶振不良。原因如下: 在晶振使用过程中,若晶振经过焊接后出现大批量的不良现象,很大一部分原因是焊接温度过高或/及焊接时间过长,…

为什么高温焊接可能会造成石英晶振不良?

2021-07-21在石英晶片的两个对应面背银作为电极,由电极焊接引线至管脚,气密性封装外壳(真空并充氮气),这样就制造出石英晶体谐振器,简称石英晶振或晶振。 若晶振高温焊接方法不当,会直接造成晶振不良。原因如下: 在晶振使用过程中,若晶振经过焊接后出现大批量的不良现象,很大一部分原因是焊接温度过高或/及焊接时间过长,… -

; ) 关于晶振偶次谐波干扰问题的三点建议

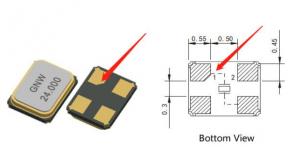

2021-07-16(晶诺威科技贴片晶振产品) 首先说明,以下内容主要针对后期产品进行整改的办法。如果在PCB布线设计初期,可以从电路板的结构设计上进行更改,这样更有效。 基于PCB设计及布线可能存在的复杂性及/或不合理性,我们有时会遇到晶振谐波干扰的问题,建议从以下三个方面考虑: 1、如果针对被干扰的设备采取防电磁干…

关于晶振偶次谐波干扰问题的三点建议

2021-07-16(晶诺威科技贴片晶振产品) 首先说明,以下内容主要针对后期产品进行整改的办法。如果在PCB布线设计初期,可以从电路板的结构设计上进行更改,这样更有效。 基于PCB设计及布线可能存在的复杂性及/或不合理性,我们有时会遇到晶振谐波干扰的问题,建议从以下三个方面考虑: 1、如果针对被干扰的设备采取防电磁干… -

; ) PCB温测时晶振停振或频偏超差怎么办?

2021-07-14晶振温测建议: 1、至少10度一点 2、温度从低到高单循环测试 3、以常温25度归零 在针对PCB过高低温测试时,当晶振停振或晶振温漂超差现象发生时: 1、从PCB板取下晶振,针对该晶振单体的频率精度及电阻进行测试,确认晶振是否停振或电阻超差。 2、确认晶振是否符合高低温要求,如温度频…

PCB温测时晶振停振或频偏超差怎么办?

2021-07-14晶振温测建议: 1、至少10度一点 2、温度从低到高单循环测试 3、以常温25度归零 在针对PCB过高低温测试时,当晶振停振或晶振温漂超差现象发生时: 1、从PCB板取下晶振,针对该晶振单体的频率精度及电阻进行测试,确认晶振是否停振或电阻超差。 2、确认晶振是否符合高低温要求,如温度频… -

; ) 如何使用万用表测晶振?万能表能测出晶振好坏吗?

2021-07-08如何使用万能表测试晶振,这里提及的晶振通常指的是无源晶振,举例如下(也是诸多工程师常用手法): 1、打开万用表,把万用表旋钮箭头旋到直流电压20档位,红表笔插到电压孔,黑表笔插到接地孔(GND)。 2、然后准备好待测试的电路板,找到晶振的两个管脚(即频率输入脚与频率输出脚)。 3、测试点1:把黑表笔…

如何使用万用表测晶振?万能表能测出晶振好坏吗?

2021-07-08如何使用万能表测试晶振,这里提及的晶振通常指的是无源晶振,举例如下(也是诸多工程师常用手法): 1、打开万用表,把万用表旋钮箭头旋到直流电压20档位,红表笔插到电压孔,黑表笔插到接地孔(GND)。 2、然后准备好待测试的电路板,找到晶振的两个管脚(即频率输入脚与频率输出脚)。 3、测试点1:把黑表笔… -

; ) 在晶振电路中如何选择外接电容

2021-07-05电容是什么? 电容(Capacitance)亦称作“电容量”,是指在给定电位差下的电荷储藏量,记为C,国际单位是法拉(F)。一般来说,电荷在电场中会受力而移动,当导体之间有了介质,则阻碍了电荷移动而使得电荷累积在导体上,造成电荷的累积储存,储存的电荷量则称为电容。电容是指容纳电场的能力。任何静电场都…

在晶振电路中如何选择外接电容

2021-07-05电容是什么? 电容(Capacitance)亦称作“电容量”,是指在给定电位差下的电荷储藏量,记为C,国际单位是法拉(F)。一般来说,电荷在电场中会受力而移动,当导体之间有了介质,则阻碍了电荷移动而使得电荷累积在导体上,造成电荷的累积储存,储存的电荷量则称为电容。电容是指容纳电场的能力。任何静电场都… -

; ) 为何晶振会在实际应用中会出现频率偏差现象?

2021-06-24在晶振量产制造中,晶振自身产生的标准内的频率偏差是正常的。而在晶振实际应用中,也同样会出现频率偏差现象。晶振生产厂家能做到的是尽量将晶振偏差控制到最小。一般晶振频率偏差范围为±10ppm ~ ±30ppm。 晶振精度的重要性 频率稳定性:晶振的精度体现在其频率稳定性上。频率稳定性直接影响设备的性能,…

为何晶振会在实际应用中会出现频率偏差现象?

2021-06-24在晶振量产制造中,晶振自身产生的标准内的频率偏差是正常的。而在晶振实际应用中,也同样会出现频率偏差现象。晶振生产厂家能做到的是尽量将晶振偏差控制到最小。一般晶振频率偏差范围为±10ppm ~ ±30ppm。 晶振精度的重要性 频率稳定性:晶振的精度体现在其频率稳定性上。频率稳定性直接影响设备的性能,…

; )