-

; ) 上板测试为何晶振不起振?

2021-04-13上板测试为何晶振不起振原因分析: 通常振荡电路在设计时会有一个负性阻抗,这个负性阻抗通常会与电路的反馈系数、有源元件的放大倍数有关。 石英谐振器(无源晶振)作为选频元件,本身有一个等效的谐振电阻。这个谐振电阻与谐振器的封装尺寸、频率有关,通常谐振器尺寸越小,谐振电阻越大;频率越低,谐振电阻越大。 当…

上板测试为何晶振不起振?

2021-04-13上板测试为何晶振不起振原因分析: 通常振荡电路在设计时会有一个负性阻抗,这个负性阻抗通常会与电路的反馈系数、有源元件的放大倍数有关。 石英谐振器(无源晶振)作为选频元件,本身有一个等效的谐振电阻。这个谐振电阻与谐振器的封装尺寸、频率有关,通常谐振器尺寸越小,谐振电阻越大;频率越低,谐振电阻越大。 当… -

; ) 无功功率和谐波的危害及影响

2021-04-10关于无功功率和谐波的危害及影响,晶诺威科技介绍如下: 1、无功功率的影响 无功功率的增加,会导致电流增大和视在功率增加,从而使发电机、变压器及其他电气设备容量和导线容量增加。同时,电力用户的起动及控制设备、测量仪表的尺寸和规格也要加大。 无功功率的增加,使总电流增大,因而使设备及线路的损耗增加,这是…

无功功率和谐波的危害及影响

2021-04-10关于无功功率和谐波的危害及影响,晶诺威科技介绍如下: 1、无功功率的影响 无功功率的增加,会导致电流增大和视在功率增加,从而使发电机、变压器及其他电气设备容量和导线容量增加。同时,电力用户的起动及控制设备、测量仪表的尺寸和规格也要加大。 无功功率的增加,使总电流增大,因而使设备及线路的损耗增加,这是… -

; ) 上板上电测试晶振波形不稳原因分析及解决方法

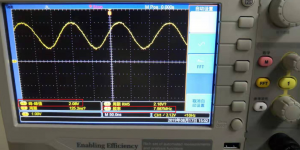

2021-04-08无源晶振波形不稳原因一 在石英谐振器(无源晶振)起振过程中,IC温度也会逐渐上升,带动整体电路板的温度同步上升。在电路板上对温度敏感的元器件除了石英晶振,还有电容,电感,电阻等相关的电子元器件,因此可能为这些元器件随着温度上升后发生改变,导致杂散电容CS发生变化,从而抓不到主频。 建议解决方法: 石…

上板上电测试晶振波形不稳原因分析及解决方法

2021-04-08无源晶振波形不稳原因一 在石英谐振器(无源晶振)起振过程中,IC温度也会逐渐上升,带动整体电路板的温度同步上升。在电路板上对温度敏感的元器件除了石英晶振,还有电容,电感,电阻等相关的电子元器件,因此可能为这些元器件随着温度上升后发生改变,导致杂散电容CS发生变化,从而抓不到主频。 建议解决方法: 石… -

; ) 负性阻抗测试方法介绍

2021-04-07关于无源晶振起振电路中的负性阻抗测试方法,晶诺威科技介绍如下: 负性阻抗概念 英文:Negative Impedance/Negative Resistance 指振荡电路需要满足无源晶振起振并保持稳定输出频率的阻抗特性值。我们通常参考无源晶振的两个功能性引脚(频率输出脚与频率输入脚)朝向的振荡电路…

负性阻抗测试方法介绍

2021-04-07关于无源晶振起振电路中的负性阻抗测试方法,晶诺威科技介绍如下: 负性阻抗概念 英文:Negative Impedance/Negative Resistance 指振荡电路需要满足无源晶振起振并保持稳定输出频率的阻抗特性值。我们通常参考无源晶振的两个功能性引脚(频率输出脚与频率输入脚)朝向的振荡电路… -

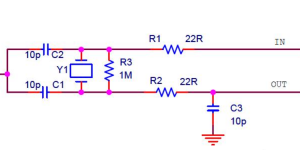

; ) 无源晶振起振电路图,无源晶振起振电路解析与无源晶振起振电路电容使用说明

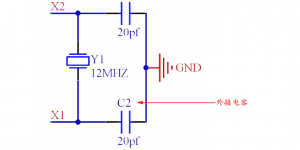

2021-04-03(无源晶振起振电路图) 无源晶振起振电路图备注: 1、C1、C2为外接电容,根据与晶振负载电容匹配程度选值 2、R1、R2可以根据实际情况调整磁珠阻抗的大小 3、C3为预设计,可根据测试情况增加或者降低 4、C1/C2可根据测试情况进行大小调整 在无源晶振实际使用中,我们经常遇到的问题一般有两点:…

无源晶振起振电路图,无源晶振起振电路解析与无源晶振起振电路电容使用说明

2021-04-03(无源晶振起振电路图) 无源晶振起振电路图备注: 1、C1、C2为外接电容,根据与晶振负载电容匹配程度选值 2、R1、R2可以根据实际情况调整磁珠阻抗的大小 3、C3为预设计,可根据测试情况增加或者降低 4、C1/C2可根据测试情况进行大小调整 在无源晶振实际使用中,我们经常遇到的问题一般有两点:… -

; ) 关于无源晶振起振电路设计注意事项

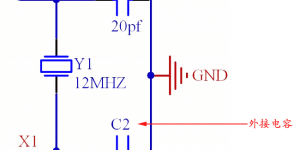

2021-04-02在无源晶振起振电路设计时,我们应当注意以下三点: 对地电容(外接电容) 如果在无源晶振振荡电路中对地电容(外接电容)与无源晶振本身负载电容(CL)没有做到最佳匹配,可能导致振荡频率与设计频率(目标频率)之间产生偏差,即我们所说的“频偏”。 在无源晶振振荡电路中,晶振负载电容、杂散电容与对地电容之间的…

关于无源晶振起振电路设计注意事项

2021-04-02在无源晶振起振电路设计时,我们应当注意以下三点: 对地电容(外接电容) 如果在无源晶振振荡电路中对地电容(外接电容)与无源晶振本身负载电容(CL)没有做到最佳匹配,可能导致振荡频率与设计频率(目标频率)之间产生偏差,即我们所说的“频偏”。 在无源晶振振荡电路中,晶振负载电容、杂散电容与对地电容之间的… -

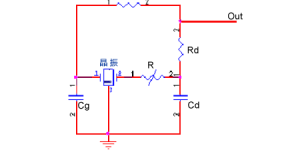

; ) 有源晶振EMC标准电路设计

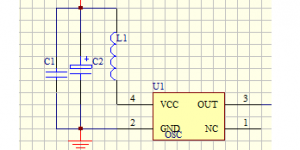

2021-03-31(有源晶振EMC标准电路) 在有源晶振EMC标准电路设计时,如果对EMC要求不高,可以去掉L1磁珠及C1负载电容,只保留电源输入端的去耦电容,取0.1uf即可,输出端保留输出电阻,约10Ω~27Ω。 具体操作如下: 1、电源端磁珠L1与电容C2、C3构成LC滤波电路。 2、信号输出端串联电阻是为了减…

有源晶振EMC标准电路设计

2021-03-31(有源晶振EMC标准电路) 在有源晶振EMC标准电路设计时,如果对EMC要求不高,可以去掉L1磁珠及C1负载电容,只保留电源输入端的去耦电容,取0.1uf即可,输出端保留输出电阻,约10Ω~27Ω。 具体操作如下: 1、电源端磁珠L1与电容C2、C3构成LC滤波电路。 2、信号输出端串联电阻是为了减… -

; ) 晶振输出频率异常怎么办?

2021-03-30晶振在数码产品及智能设备中的应用已经相当普及,因此晶振在实际电路应用中往往也出现许多问题,比如晶振实际输出频率异常,包括无频率信号输出或输出频率信号与标称频率存在严重差异。 原因如下: 实际激励功率超出晶振指定范围 负载电容与规范中指定值存在差异 外接电容与晶振负载电容不匹配 晶振精度与IC指定值不…

晶振输出频率异常怎么办?

2021-03-30晶振在数码产品及智能设备中的应用已经相当普及,因此晶振在实际电路应用中往往也出现许多问题,比如晶振实际输出频率异常,包括无频率信号输出或输出频率信号与标称频率存在严重差异。 原因如下: 实际激励功率超出晶振指定范围 负载电容与规范中指定值存在差异 外接电容与晶振负载电容不匹配 晶振精度与IC指定值不… -

; ) 怎样设计一个无源晶振电路?

2021-03-29无源晶振电路设计方法建议如下: (1)让晶振,外部电容器与IC之间的信号线尽可能保持最短。当非常低的电流通过晶振时,若线路太长,会造成更多电磁干扰对晶振的影响,同时寄生电容也会增加,影响晶振频率精度。 (2)需要特别注意晶振和地的走线。 (3)晶振位置尽可能要远离时钟线路和频繁切换的信号线。 (4)…

怎样设计一个无源晶振电路?

2021-03-29无源晶振电路设计方法建议如下: (1)让晶振,外部电容器与IC之间的信号线尽可能保持最短。当非常低的电流通过晶振时,若线路太长,会造成更多电磁干扰对晶振的影响,同时寄生电容也会增加,影响晶振频率精度。 (2)需要特别注意晶振和地的走线。 (3)晶振位置尽可能要远离时钟线路和频繁切换的信号线。 (4)… -

; ) 晶体谐振器的激励电平和激励功率的区别是什么?

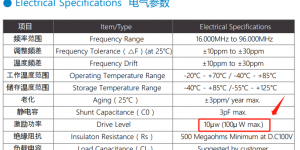

2021-03-19晶体谐振器的激励电平和激励功率的区别是什么?解释如下: 首先“激励电平”或“激励功率”这两个术语主要是专门针对无源晶振电路应用而言的。 名词解释: 晶体谐振器 中文别称:无源晶振,晶振,晶体,谐振器,石英谐振器 全称:石英晶体谐振器 英文名称:Crystal 英文简称Xtal 激励电平 英文名称:D…

晶体谐振器的激励电平和激励功率的区别是什么?

2021-03-19晶体谐振器的激励电平和激励功率的区别是什么?解释如下: 首先“激励电平”或“激励功率”这两个术语主要是专门针对无源晶振电路应用而言的。 名词解释: 晶体谐振器 中文别称:无源晶振,晶振,晶体,谐振器,石英谐振器 全称:石英晶体谐振器 英文名称:Crystal 英文简称Xtal 激励电平 英文名称:D…