-

; ) 关于晶振DLD不良的解释

2025-04-22关于晶振DLD不良问题,晶诺威科技解释如下: 晶振DLD不良通常是指晶振在测试或使用过程中出现“驱动电平依赖性”(Drive Level Dependency,DLD)问题。DLD是晶振的一个重要参数,表示晶振的输出频率或特性随驱动电平的变化而变化。如果DLD不良,可能会导致晶振的频率稳定性变差,影…

关于晶振DLD不良的解释

2025-04-22关于晶振DLD不良问题,晶诺威科技解释如下: 晶振DLD不良通常是指晶振在测试或使用过程中出现“驱动电平依赖性”(Drive Level Dependency,DLD)问题。DLD是晶振的一个重要参数,表示晶振的输出频率或特性随驱动电平的变化而变化。如果DLD不良,可能会导致晶振的频率稳定性变差,影… -

; ) 4MHz晶振坏了会有什么现象?

2025-04-214MHz晶振坏了会有什么现象? 答:4MHz晶振损坏可能导致以下现象: 1、系统无法启动 晶振为微控制器或处理器提供时钟信号,损坏后设备可能无法启动或运行。 2、功能异常 时钟信号不稳定会导致设备运行异常,如程序卡顿、响应迟缓或功能失效。 3、通信故障 依赖时钟信号的通信接口(如UART、SPI、I…

4MHz晶振坏了会有什么现象?

2025-04-214MHz晶振坏了会有什么现象? 答:4MHz晶振损坏可能导致以下现象: 1、系统无法启动 晶振为微控制器或处理器提供时钟信号,损坏后设备可能无法启动或运行。 2、功能异常 时钟信号不稳定会导致设备运行异常,如程序卡顿、响应迟缓或功能失效。 3、通信故障 依赖时钟信号的通信接口(如UART、SPI、I… -

; ) 晶体谐振器的起振电容通常取值范围是多少?

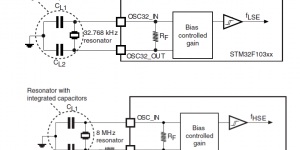

2025-04-20晶体谐振器的起振电容通常取值范围是多少? 答:晶体谐振器(无源晶振)起振电容一般在几皮法(pF)到几十皮法之间,常用范围为10pF至30pF。 注意: 1、具体值需根据晶体的负载电容要求选择。 2、实际应用中,需根据电路设计和元件参数选择合适的电容值,必要时通过实验调整以达到最佳效果。

晶体谐振器的起振电容通常取值范围是多少?

2025-04-20晶体谐振器的起振电容通常取值范围是多少? 答:晶体谐振器(无源晶振)起振电容一般在几皮法(pF)到几十皮法之间,常用范围为10pF至30pF。 注意: 1、具体值需根据晶体的负载电容要求选择。 2、实际应用中,需根据电路设计和元件参数选择合适的电容值,必要时通过实验调整以达到最佳效果。 -

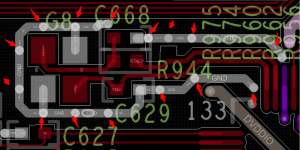

; ) 关于SMD3225晶振布线说明

2025-04-18关于SMD3225晶振布线设计,晶诺威科技说明如下: SMD3225晶振是一种表面贴装(SMD)封装的石英晶体振荡器,尺寸为3.2mm × 2.5mm。它在高频电路中广泛应用,如通信设备、消费电子和工业控制等。为了确保SMD3225晶振的正常工作和稳定性,PCB布线设计非常关键。以下是SMD3225…

关于SMD3225晶振布线说明

2025-04-18关于SMD3225晶振布线设计,晶诺威科技说明如下: SMD3225晶振是一种表面贴装(SMD)封装的石英晶体振荡器,尺寸为3.2mm × 2.5mm。它在高频电路中广泛应用,如通信设备、消费电子和工业控制等。为了确保SMD3225晶振的正常工作和稳定性,PCB布线设计非常关键。以下是SMD3225… -

; ) 晶振的负载是不是越大越好?

2025-04-13晶振的负载是不是越大越好? 答:负载电容的选择需根据晶振规格和电路需求,过大或过小都会影响性能。 关于晶振负载大小的问题,晶诺威科技进一步解释如下: 晶振的负载并不是越大越好,负载电容的选择需要根据晶振的特性和电路设计要求来确定。以下是关键点: 负载电容的作用 负载电容用于调整晶振的振荡频率,确保其…

晶振的负载是不是越大越好?

2025-04-13晶振的负载是不是越大越好? 答:负载电容的选择需根据晶振规格和电路需求,过大或过小都会影响性能。 关于晶振负载大小的问题,晶诺威科技进一步解释如下: 晶振的负载并不是越大越好,负载电容的选择需要根据晶振的特性和电路设计要求来确定。以下是关键点: 负载电容的作用 负载电容用于调整晶振的振荡频率,确保其… -

; ) 信号线到晶振的距离是多少?

2025-04-10信号线到晶振的距离是多少? 答:距离越短越好,通常不超过5厘米,高频应用需更短。 信号线到晶振的距离应尽可能短,以减少噪声和信号完整性问题。晶诺威科技具体建议如下: 一般建议: 距离最好控制在 5厘米 以内。 高频应用: 在高频电路中,距离应进一步缩短,通常小于 2.5厘米。 布局优化: 信号线应直…

信号线到晶振的距离是多少?

2025-04-10信号线到晶振的距离是多少? 答:距离越短越好,通常不超过5厘米,高频应用需更短。 信号线到晶振的距离应尽可能短,以减少噪声和信号完整性问题。晶诺威科技具体建议如下: 一般建议: 距离最好控制在 5厘米 以内。 高频应用: 在高频电路中,距离应进一步缩短,通常小于 2.5厘米。 布局优化: 信号线应直… -

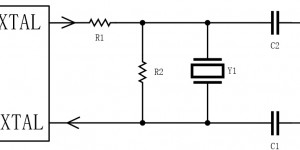

; ) 无源晶振的匹配电容不一致可能导致什么问题?

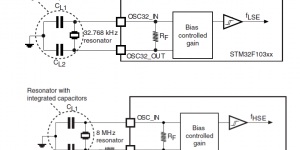

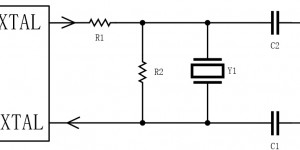

2025-04-07无源晶振的匹配电容不一致可能导致什么问题? 答:无源晶振的匹配电容不一致会导致频率偏移、启动困难或信号不稳定。 解决方法包括: 按照芯片数据手册设计匹配电容。 测量并确保电容值准确。 优化焊接和PCB布局。 必要时通过调试调整电容值。负载电容计算公式如下: 为了增加无源晶振振荡电路的稳定性,建议C1…

无源晶振的匹配电容不一致可能导致什么问题?

2025-04-07无源晶振的匹配电容不一致可能导致什么问题? 答:无源晶振的匹配电容不一致会导致频率偏移、启动困难或信号不稳定。 解决方法包括: 按照芯片数据手册设计匹配电容。 测量并确保电容值准确。 优化焊接和PCB布局。 必要时通过调试调整电容值。负载电容计算公式如下: 为了增加无源晶振振荡电路的稳定性,建议C1… -

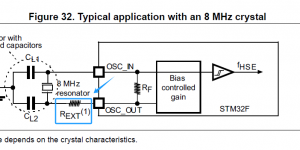

; ) 无源晶振串联0欧姆电阻串联在哪里?

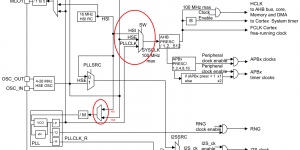

2025-04-06(无源晶振电路中0欧姆串联电阻位置:Rext处) 无源晶振串联0欧姆电阻串联在哪里? 答:0欧姆串联电阻通常位于晶振与微控制器时钟信号输出脚之间。 串联0欧姆电阻具体位置如下: 晶振频率管脚:电阻的一端连接晶振的其中一个频率引脚。 芯片时钟信号输出脚:电阻的另一端连接微控制器的时钟输出引脚(OSC_…

无源晶振串联0欧姆电阻串联在哪里?

2025-04-06(无源晶振电路中0欧姆串联电阻位置:Rext处) 无源晶振串联0欧姆电阻串联在哪里? 答:0欧姆串联电阻通常位于晶振与微控制器时钟信号输出脚之间。 串联0欧姆电阻具体位置如下: 晶振频率管脚:电阻的一端连接晶振的其中一个频率引脚。 芯片时钟信号输出脚:电阻的另一端连接微控制器的时钟输出引脚(OSC_… -

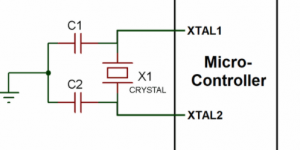

; ) 晶振电容不等值选取会怎么样?

2025-04-03晶振电容不等值选取会怎么样? 答:晶振电容不等值选取会导致频率偏差、起振困难、稳定性下降、功耗增加和EMI问题。通过参考晶振规格书、等值选取、使用高精度电容和优化电路布局,可以减少这些影响,确保电路稳定运行。 建议:C1=C2

晶振电容不等值选取会怎么样?

2025-04-03晶振电容不等值选取会怎么样? 答:晶振电容不等值选取会导致频率偏差、起振困难、稳定性下降、功耗增加和EMI问题。通过参考晶振规格书、等值选取、使用高精度电容和优化电路布局,可以减少这些影响,确保电路稳定运行。 建议:C1=C2 -

; ) 无源晶振必须有一脚接地吗?

2025-04-01无源晶振必须有一脚接地吗? 答:通常情况下,无源晶振不一定必须有一脚接地,具体取决于电路设计。 以下是常见情况: 两脚无源晶振:通常一脚接振荡电路的输入端,另一脚接输出端。 四脚无源晶振:通常两脚为晶振引脚,另两脚为接地引脚,用于屏蔽和稳定性。 接地的作用 提高稳定性:接地可减少干扰,提升振荡稳定性…

无源晶振必须有一脚接地吗?

2025-04-01无源晶振必须有一脚接地吗? 答:通常情况下,无源晶振不一定必须有一脚接地,具体取决于电路设计。 以下是常见情况: 两脚无源晶振:通常一脚接振荡电路的输入端,另一脚接输出端。 四脚无源晶振:通常两脚为晶振引脚,另两脚为接地引脚,用于屏蔽和稳定性。 接地的作用 提高稳定性:接地可减少干扰,提升振荡稳定性…