-

; ) 电子设计中的EMI和EMC有什么区别?

2024-06-10(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…

电子设计中的EMI和EMC有什么区别?

2024-06-10(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele… -

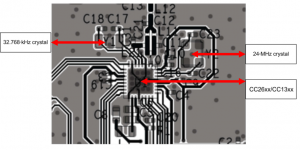

; ) 如何最大程度减少晶振电路中的串扰信号及EMI?

2024-06-08如何最大程度减少晶振电路中的串扰信号及EMI?晶诺威科技解答如下: ( Low-Frequency Oscillator with Quartz Crystal 32.768KHz) As is shown above,The oscillator circuit consists of an in…

如何最大程度减少晶振电路中的串扰信号及EMI?

2024-06-08如何最大程度减少晶振电路中的串扰信号及EMI?晶诺威科技解答如下: ( Low-Frequency Oscillator with Quartz Crystal 32.768KHz) As is shown above,The oscillator circuit consists of an in… -

; ) 晶振电路故障检测及排除方法

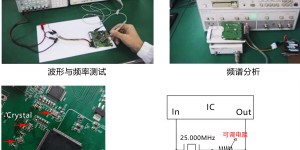

2024-06-08关于对晶振单体判定的方法,晶诺威科技归纳四点如下: 1、测电压: 使用万用表直流电压档测量晶振两端的电压。正常起振时,电压应接近芯片供电电压VCC的一半。如果发现晶振两端的电压有明显偏差,例如一边接近VCC或接近0V,这可能表明晶振没有起振。 2、观察波形: 使用示波器观察晶振两端的波形。起振时,应…

晶振电路故障检测及排除方法

2024-06-08关于对晶振单体判定的方法,晶诺威科技归纳四点如下: 1、测电压: 使用万用表直流电压档测量晶振两端的电压。正常起振时,电压应接近芯片供电电压VCC的一半。如果发现晶振两端的电压有明显偏差,例如一边接近VCC或接近0V,这可能表明晶振没有起振。 2、观察波形: 使用示波器观察晶振两端的波形。起振时,应… -

; ) 433无线射频模组晶振频率为何是13.52127MHz?

2024-06-06(无线门铃及可视对讲系统) 433无线射频模组晶振频率为何是13.52127MHz? 答:13.52127*32=432.68064≈433 由此可见,13.52127MHz通过32次倍频,可以获取433MHz这个频率段。同理,6.7458MHz通过64次倍频同样也可以获取433MHz这个频率段。因…

433无线射频模组晶振频率为何是13.52127MHz?

2024-06-06(无线门铃及可视对讲系统) 433无线射频模组晶振频率为何是13.52127MHz? 答:13.52127*32=432.68064≈433 由此可见,13.52127MHz通过32次倍频,可以获取433MHz这个频率段。同理,6.7458MHz通过64次倍频同样也可以获取433MHz这个频率段。因… -

; ) RF晶振频偏会影响发射功率吗?

2024-06-04(RF connection failed) RF晶振频偏会影响发射功率吗? 答:在RF射频设备中,一旦晶振频偏超差,容易导致信号发射端与接收端之间不联机、连机困难或发射距离变短等问题。 无源晶振在实际工作中发生频偏现象,受到多种因素影响,如晶振本身频率精度(如:±10ppm)、电路匹配(布线、匹配…

RF晶振频偏会影响发射功率吗?

2024-06-04(RF connection failed) RF晶振频偏会影响发射功率吗? 答:在RF射频设备中,一旦晶振频偏超差,容易导致信号发射端与接收端之间不联机、连机困难或发射距离变短等问题。 无源晶振在实际工作中发生频偏现象,受到多种因素影响,如晶振本身频率精度(如:±10ppm)、电路匹配(布线、匹配… -

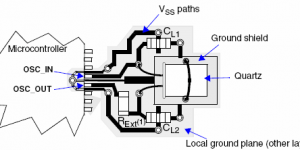

; ) 关于无源晶振电路中外接电容CL1和CL2的选取

2024-06-02关于无源晶振电路中外接电容CL1和CL2的选取,晶诺威科技解释如下: 英文解释: For CL1 and CL2,it is recommended to use high quality ceramic dielectric capacitance (typically) between 5pF …

关于无源晶振电路中外接电容CL1和CL2的选取

2024-06-02关于无源晶振电路中外接电容CL1和CL2的选取,晶诺威科技解释如下: 英文解释: For CL1 and CL2,it is recommended to use high quality ceramic dielectric capacitance (typically) between 5pF … -

; ) Equivalent Series Resistance of the Crystal 晶体的等效电阻

2024-06-01英文解释: The equivalent series resistance of the crystal must be within the specifications so that the crystal can have a reliable vibration. 中文解释: 晶体谐振器…

Equivalent Series Resistance of the Crystal 晶体的等效电阻

2024-06-01英文解释: The equivalent series resistance of the crystal must be within the specifications so that the crystal can have a reliable vibration. 中文解释: 晶体谐振器… -

; ) 降低EMI电磁干扰及解决EMC辐射超标问题的钥匙:展频晶振

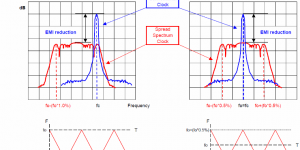

2024-05-27(EMI REDUCTION VIA DOWN SPREAD AND CENTER SPREAD) 目前,EMC电磁兼容性对于RF射频类电子设备要求越来越高,如何降低EMI电磁干扰已经成为我们进行产品设计的重中之重。 通常情况下,与EMI电磁干扰密切相关的主要是:时钟、电源、布线、屏蔽等,这些都可能…

降低EMI电磁干扰及解决EMC辐射超标问题的钥匙:展频晶振

2024-05-27(EMI REDUCTION VIA DOWN SPREAD AND CENTER SPREAD) 目前,EMC电磁兼容性对于RF射频类电子设备要求越来越高,如何降低EMI电磁干扰已经成为我们进行产品设计的重中之重。 通常情况下,与EMI电磁干扰密切相关的主要是:时钟、电源、布线、屏蔽等,这些都可能… -

; ) 外接电容选择不当会对晶振电路造成什么影响?

2024-05-25外接电容选择不当会对晶振电路造成什么影响? 如果晶振的外接电容值选择不当,可能会对电路产生以下影响: 1、频率稳定性:电容值过小可能导致频率稳定性下降,容易受到外界因素的干扰。电容值过大可能会使频率偏离标称值。 2、起振问题:电容值不合适可能导致晶振无法正常起振或起振困难。 3、功耗增加:不恰当的电…

外接电容选择不当会对晶振电路造成什么影响?

2024-05-25外接电容选择不当会对晶振电路造成什么影响? 如果晶振的外接电容值选择不当,可能会对电路产生以下影响: 1、频率稳定性:电容值过小可能导致频率稳定性下降,容易受到外界因素的干扰。电容值过大可能会使频率偏离标称值。 2、起振问题:电容值不合适可能导致晶振无法正常起振或起振困难。 3、功耗增加:不恰当的电… -

; ) RF射频设备晶振频偏会导致射频距离变短吗?

2024-05-20RF射频设备晶振频偏会导致射频距离变短吗? 答:是的,晶振频偏会直接影响RF射频距离。如果蓝牙晶振选型或使用不当,例如100米信号发射及接收距离可能缩短,如50米。 (Bluetooth Tacking Distance) 关于RF射频设备信号传输距离,在晶振选型方面,晶诺威科技解释如下: 1、 请…

RF射频设备晶振频偏会导致射频距离变短吗?

2024-05-20RF射频设备晶振频偏会导致射频距离变短吗? 答:是的,晶振频偏会直接影响RF射频距离。如果蓝牙晶振选型或使用不当,例如100米信号发射及接收距离可能缩短,如50米。 (Bluetooth Tacking Distance) 关于RF射频设备信号传输距离,在晶振选型方面,晶诺威科技解释如下: 1、 请…