-

; ) 造成有源晶振损坏的最常见三个因素

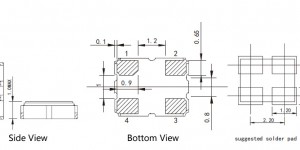

2023-04-27(晶诺威产有源晶振OSC3225尺寸及焊盘说明) 关于造成有源晶振损坏的最常见三个因素,说明如下: 1、脚位焊接错误 必须把电压输入接到晶振的电压输入脚(VCC或VDD)。若错接到接地脚,晶振就会被电流“烧坏”。晶诺威科技产有源晶振的丝印左下有个圆点,底部对应的则是脚1。 2、电压超载 有源晶振常用…

造成有源晶振损坏的最常见三个因素

2023-04-27(晶诺威产有源晶振OSC3225尺寸及焊盘说明) 关于造成有源晶振损坏的最常见三个因素,说明如下: 1、脚位焊接错误 必须把电压输入接到晶振的电压输入脚(VCC或VDD)。若错接到接地脚,晶振就会被电流“烧坏”。晶诺威科技产有源晶振的丝印左下有个圆点,底部对应的则是脚1。 2、电压超载 有源晶振常用… -

; ) 晶诺威产三引线晶振引脚使用说明

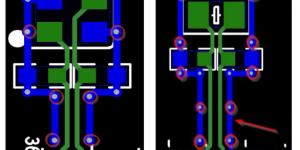

2023-04-26晶诺威产三引线晶振引脚使用说明如下: 三引线晶振属于无源晶振,两侧脚为频率管脚,没有方向之分。三引线晶振中间引脚为接地脚,请在电路中接GND。 三引线晶振的中间引线如下图红色箭头所示: 三引线晶振中间引线的作用: 降低周边电路对晶振的干扰,确保晶振稳定工作。 注: 为了进一步增强对晶振信号的屏蔽性,…

晶诺威产三引线晶振引脚使用说明

2023-04-26晶诺威产三引线晶振引脚使用说明如下: 三引线晶振属于无源晶振,两侧脚为频率管脚,没有方向之分。三引线晶振中间引脚为接地脚,请在电路中接GND。 三引线晶振的中间引线如下图红色箭头所示: 三引线晶振中间引线的作用: 降低周边电路对晶振的干扰,确保晶振稳定工作。 注: 为了进一步增强对晶振信号的屏蔽性,… -

; ) 晶振振荡电路中的负阻一般多大?

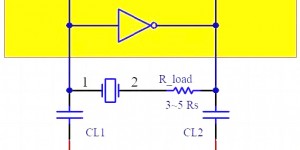

2023-04-25晶振振荡电路中的负阻一般多大? 答:若要获得稳定的振荡电路,振荡电路IC的负电阻值(-R)至少为晶振等效阻抗的3~5倍以上,即绝对值|-R|>3~5*R。 举例来说: 如果晶振电路阻抗总值为30Ω,那么,我们建议IC的负电阻值需要至少在-150Ω,这样才能有效保障振荡回路的稳定性。

晶振振荡电路中的负阻一般多大?

2023-04-25晶振振荡电路中的负阻一般多大? 答:若要获得稳定的振荡电路,振荡电路IC的负电阻值(-R)至少为晶振等效阻抗的3~5倍以上,即绝对值|-R|>3~5*R。 举例来说: 如果晶振电路阻抗总值为30Ω,那么,我们建议IC的负电阻值需要至少在-150Ω,这样才能有效保障振荡回路的稳定性。 -

; ) 关于晶振频偏导致LoRa丢数据包问题的解析

2023-04-24关于晶振频偏导致LoRa丢数据包问题,晶诺威科技解析如下: 不管是蓝牙,WiFi还是LoRa,在数据无线传输时,晶振频偏超差会造成数据包丢失。原理是:数据以电压转换为频率,再以频率发射,频偏意味着一些数据无法正确抵达接收端。 打一个比方,这类似于你网购了一些物资,这些物资分成了10个包裹发送给你。结…

关于晶振频偏导致LoRa丢数据包问题的解析

2023-04-24关于晶振频偏导致LoRa丢数据包问题,晶诺威科技解析如下: 不管是蓝牙,WiFi还是LoRa,在数据无线传输时,晶振频偏超差会造成数据包丢失。原理是:数据以电压转换为频率,再以频率发射,频偏意味着一些数据无法正确抵达接收端。 打一个比方,这类似于你网购了一些物资,这些物资分成了10个包裹发送给你。结… -

; ) 如何尽量避免晶振虚焊问题?

2023-04-22如何尽量避免晶振虚焊问题? 晶振引脚或焊盘虚焊会造成电路出现时通时断现象,造成晶振时振时不振不良现象的假象。造成晶振虚焊原因主要有以下三方面: 晶振本身品质 因晶振引脚或焊盘出现不同程度氧化现象、电镀层脱落或焊盘不平整(主要出现在晶振49SMD封装),焊接时增加引脚/焊盘吃锡困难,引发虚焊。晶振的储…

如何尽量避免晶振虚焊问题?

2023-04-22如何尽量避免晶振虚焊问题? 晶振引脚或焊盘虚焊会造成电路出现时通时断现象,造成晶振时振时不振不良现象的假象。造成晶振虚焊原因主要有以下三方面: 晶振本身品质 因晶振引脚或焊盘出现不同程度氧化现象、电镀层脱落或焊盘不平整(主要出现在晶振49SMD封装),焊接时增加引脚/焊盘吃锡困难,引发虚焊。晶振的储… -

; ) 无源晶振容易受到杂散讯号干扰吗?

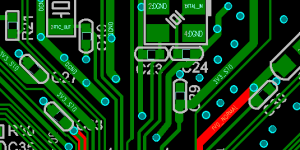

2023-04-21无源晶振容易受到杂散讯号干扰吗? 答:是的,无源晶振(晶体谐振器)的振荡电路非常容易受到周边信号干扰,造成频率不稳定。 建议晶振远离信号辐射源,如电源、天线、蜂鸣器、电机、风扇及板边等。 如果对晶振信号精度及稳定度有着高要求,也就意味着对晶振有抗干扰性有要求,建议选择三脚或四脚高精度无源晶振,而不是…

无源晶振容易受到杂散讯号干扰吗?

2023-04-21无源晶振容易受到杂散讯号干扰吗? 答:是的,无源晶振(晶体谐振器)的振荡电路非常容易受到周边信号干扰,造成频率不稳定。 建议晶振远离信号辐射源,如电源、天线、蜂鸣器、电机、风扇及板边等。 如果对晶振信号精度及稳定度有着高要求,也就意味着对晶振有抗干扰性有要求,建议选择三脚或四脚高精度无源晶振,而不是… -

; ) 振荡电路上的晶振没有信号输出怎么办?

2023-04-20振荡电路上的晶振没有信号输出怎么办? 在正确使用示波器或频率计数器检测晶振时,若发现晶振(这里指的是晶体谐振器/无源晶振)两个引脚没有频率信号输出,建议如下: 1、请检查晶振频率输入引脚(Xin)和频率输出引脚(Xout)之间的电压,并根据IC规格检查电压是否满足。若电压差为0,说明没有电流经过晶振…

振荡电路上的晶振没有信号输出怎么办?

2023-04-20振荡电路上的晶振没有信号输出怎么办? 在正确使用示波器或频率计数器检测晶振时,若发现晶振(这里指的是晶体谐振器/无源晶振)两个引脚没有频率信号输出,建议如下: 1、请检查晶振频率输入引脚(Xin)和频率输出引脚(Xout)之间的电压,并根据IC规格检查电压是否满足。若电压差为0,说明没有电流经过晶振… -

; ) 关于32.768KHz晶振时好时坏问题

2023-04-19关于32.768KHz晶振时好时坏问题,分析如下: 如果发现32.768KHz晶振时好时坏,不管是晶振本身问题,还是电路应用问题,都说明它没有稳定工作。 建议从以下五方面着手排查: 排查晶振引脚接入电路是否虚焊。 找到芯片数据手册关于32.768KHz晶振说明部分,逐一查看并确认晶振负载(CL)、等…

关于32.768KHz晶振时好时坏问题

2023-04-19关于32.768KHz晶振时好时坏问题,分析如下: 如果发现32.768KHz晶振时好时坏,不管是晶振本身问题,还是电路应用问题,都说明它没有稳定工作。 建议从以下五方面着手排查: 排查晶振引脚接入电路是否虚焊。 找到芯片数据手册关于32.768KHz晶振说明部分,逐一查看并确认晶振负载(CL)、等… -

; ) 关于晶振ESR(等效阻抗)太大导致晶振不起振问题

2023-04-15关于晶振ESR(等效阻抗)太大导致晶振不起振问题,晶诺威科技解释如下: 在无源晶振起振电路中,电路负性阻抗一般要在晶振ESR(等效阻抗)的5倍以上才能保障其正常起振。但是如果因晶振品质不合格,导致其ESR过大,也会造成晶振起振困难或不起振。 晶诺威科技产SMD7050晶体谐振器ESR(等效阻抗)说明…

关于晶振ESR(等效阻抗)太大导致晶振不起振问题

2023-04-15关于晶振ESR(等效阻抗)太大导致晶振不起振问题,晶诺威科技解释如下: 在无源晶振起振电路中,电路负性阻抗一般要在晶振ESR(等效阻抗)的5倍以上才能保障其正常起振。但是如果因晶振品质不合格,导致其ESR过大,也会造成晶振起振困难或不起振。 晶诺威科技产SMD7050晶体谐振器ESR(等效阻抗)说明…

; )