-

; ) 是什么原因导致了晶振频率误差Frequency Tolerance?

2022-12-28如果想了解是什么原因导致了晶振频率误差Frequency Tolerance,首先应该清楚晶振主要分为石英晶体谐振器(无源晶振)和石英晶体振荡器(有源晶振)两大类。而晶振是这两类晶体产品的统称。 石英晶体谐振器 石英晶体谐振器是由压电石英晶体和金属封装组成,其生产工艺包括:石英切割、镀银、基座、以及…

是什么原因导致了晶振频率误差Frequency Tolerance?

2022-12-28如果想了解是什么原因导致了晶振频率误差Frequency Tolerance,首先应该清楚晶振主要分为石英晶体谐振器(无源晶振)和石英晶体振荡器(有源晶振)两大类。而晶振是这两类晶体产品的统称。 石英晶体谐振器 石英晶体谐振器是由压电石英晶体和金属封装组成,其生产工艺包括:石英切割、镀银、基座、以及… -

; ) Type-C多功能拓展坞专用晶振规格参数介绍

2022-12-27(Type-C多功能拓展坞) 扩展坞(Docking station),又称端口复制器(Port Replicator),是专为笔记本电脑设计的一种外置设备。通过复制甚至扩展笔记型计算机的端口,可使笔记本电脑与多个配件或外置设备方便的一站式连接。 在拓展坞的帮助之下,我们的手机,笔记本和办公电脑可以…

Type-C多功能拓展坞专用晶振规格参数介绍

2022-12-27(Type-C多功能拓展坞) 扩展坞(Docking station),又称端口复制器(Port Replicator),是专为笔记本电脑设计的一种外置设备。通过复制甚至扩展笔记型计算机的端口,可使笔记本电脑与多个配件或外置设备方便的一站式连接。 在拓展坞的帮助之下,我们的手机,笔记本和办公电脑可以… -

; ) 24MHz ±10ppm晶振实测频率是多少?

2022-12-2724MHz ±10ppm晶振实测频率是多少?若为有源晶振或已处于最佳匹配电路的无源晶振,实测应得到以下频率范围: 24MHz ±10ppm晶振实测频率范围:23.999760MHz~24.000240MHz 24MHz ±20ppm晶振实测频率范围:23.999520MHz~24.000480MHz…

24MHz ±10ppm晶振实测频率是多少?

2022-12-2724MHz ±10ppm晶振实测频率是多少?若为有源晶振或已处于最佳匹配电路的无源晶振,实测应得到以下频率范围: 24MHz ±10ppm晶振实测频率范围:23.999760MHz~24.000240MHz 24MHz ±20ppm晶振实测频率范围:23.999520MHz~24.000480MHz… -

; ) 为何晶振32.768KHz为电脑主板常客?

2022-12-23关于电脑RTC实时时钟32.768KHz: 32.768KHz晶振产生的振荡信号,经过分频器进行15次2分频后即可得到1Hz秒信号。因此,32.768KHz就成为了RTC时钟的标准频率。这个“1Hz”秒信号是被系统当做丈量时间的工具来使用的,因此,这把“尺子”越准,时间精度就越高。当32.768KH…

为何晶振32.768KHz为电脑主板常客?

2022-12-23关于电脑RTC实时时钟32.768KHz: 32.768KHz晶振产生的振荡信号,经过分频器进行15次2分频后即可得到1Hz秒信号。因此,32.768KHz就成为了RTC时钟的标准频率。这个“1Hz”秒信号是被系统当做丈量时间的工具来使用的,因此,这把“尺子”越准,时间精度就越高。当32.768KH… -

; ) 有源晶振对工作电源电压的要求有哪些?

2022-12-22因型号规格的多样性,有源晶振所需供电电压也有所不同,晶诺威科技归纳如下: (晶诺威科技产DIP14系列---温补晶体振荡器TCXO-DIP14) 晶诺威科技产DIP插件式封装的有源晶振:3.3V和5V。插件式有源晶振常见于半尺寸DIP8和全尺寸DIP14两种封装。信号输出模式主要为方波(CMOS)和…

有源晶振对工作电源电压的要求有哪些?

2022-12-22因型号规格的多样性,有源晶振所需供电电压也有所不同,晶诺威科技归纳如下: (晶诺威科技产DIP14系列---温补晶体振荡器TCXO-DIP14) 晶诺威科技产DIP插件式封装的有源晶振:3.3V和5V。插件式有源晶振常见于半尺寸DIP8和全尺寸DIP14两种封装。信号输出模式主要为方波(CMOS)和… -

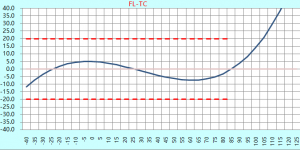

; ) 贴片晶振SMD3225-24M-9PF频率及电阻温测数据

2022-12-21(贴片晶振SMD3225-24M-9PF在温测中的频率变化) (贴片晶振SMD3225-24M-9PF在温测中的电阻变化) 贴片晶振SMD3225-24M-9PF频率及电阻温测数据如下: 针对晶振单体温测的必要性: 1、确保晶振在指定工作温度区间内没有发生电阻跳变,防止晶振起振困难或停…

贴片晶振SMD3225-24M-9PF频率及电阻温测数据

2022-12-21(贴片晶振SMD3225-24M-9PF在温测中的频率变化) (贴片晶振SMD3225-24M-9PF在温测中的电阻变化) 贴片晶振SMD3225-24M-9PF频率及电阻温测数据如下: 针对晶振单体温测的必要性: 1、确保晶振在指定工作温度区间内没有发生电阻跳变,防止晶振起振困难或停… -

; ) 车载摄像头专用有源晶体振荡器OSC3225 37.125MHz/27MHz

2022-12-20晶诺威科技产OSC3225 37.125M/27MHz是一款协助设备实现屏显功能的常用有源晶振,主要电气参数如下: 输入电压:1.8V、2.8V、3.3V或5.0V 输出类型:CMOS 总频差:±20PPM 工作温度:-40~+85℃ OSC3225 37.125M/27MHz特点及优势: 宽温、高…

车载摄像头专用有源晶体振荡器OSC3225 37.125MHz/27MHz

2022-12-20晶诺威科技产OSC3225 37.125M/27MHz是一款协助设备实现屏显功能的常用有源晶振,主要电气参数如下: 输入电压:1.8V、2.8V、3.3V或5.0V 输出类型:CMOS 总频差:±20PPM 工作温度:-40~+85℃ OSC3225 37.125M/27MHz特点及优势: 宽温、高… -

; ) 相噪与有源晶振性能之间的关系是什么?

2022-12-19相位噪声(phase noise),简称相噪,是有源晶振的一项非常重要的性能特征。它对作为振荡器的有源晶振的输出频率稳定性影响非常大,一般情况下,相位噪声越小,则表示有源晶振性能越好,输出信号稳定性越高。 相位噪声对振荡电路的影响 有源晶振的Q值对于改善相位噪声的载波频率附近的相位噪声尤其重要。无论…

相噪与有源晶振性能之间的关系是什么?

2022-12-19相位噪声(phase noise),简称相噪,是有源晶振的一项非常重要的性能特征。它对作为振荡器的有源晶振的输出频率稳定性影响非常大,一般情况下,相位噪声越小,则表示有源晶振性能越好,输出信号稳定性越高。 相位噪声对振荡电路的影响 有源晶振的Q值对于改善相位噪声的载波频率附近的相位噪声尤其重要。无论… -

; ) 关于TCXO温补晶振常见解决方案及选型注意事项

2022-12-16关于TCXO温补晶振常见解决方案及选型注意事项,总结如下: MU 指对一次互感器传输过来的电气量进行合并和同步处理,并将处理后的数字信号按照特定格式转发给间隔级设备使用的装置。 MU是电子式电流、电压互感器的接口装置。MU在一定程度上实现了过程层数据的共享和数字化,它作为遵循IEC61850标准的数…

关于TCXO温补晶振常见解决方案及选型注意事项

2022-12-16关于TCXO温补晶振常见解决方案及选型注意事项,总结如下: MU 指对一次互感器传输过来的电气量进行合并和同步处理,并将处理后的数字信号按照特定格式转发给间隔级设备使用的装置。 MU是电子式电流、电压互感器的接口装置。MU在一定程度上实现了过程层数据的共享和数字化,它作为遵循IEC61850标准的数… -

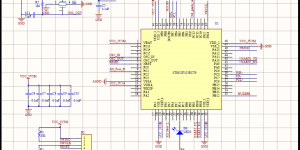

; ) 12.5PF的晶体匹配电容是多少PF?

2022-12-14匹配电容的变化对晶体输出频率的影响: 匹配电容容值增加,晶体输出频率降低。 匹配电容容值减小,晶体输出频率升高。 如果晶体负载电容CL为12.5PF,晶诺威科技建议匹配电容在15~18PF之间取值。但在晶体实际电路应用中,也有匹配22PF为最佳的情况,这主要归因于电路板本身之间的差异。 匹配电容对晶…

12.5PF的晶体匹配电容是多少PF?

2022-12-14匹配电容的变化对晶体输出频率的影响: 匹配电容容值增加,晶体输出频率降低。 匹配电容容值减小,晶体输出频率升高。 如果晶体负载电容CL为12.5PF,晶诺威科技建议匹配电容在15~18PF之间取值。但在晶体实际电路应用中,也有匹配22PF为最佳的情况,这主要归因于电路板本身之间的差异。 匹配电容对晶…