-

; ) 关于晶振起振时间太慢原因分析及解决方案

2022-07-15(无源晶振电路) 我们都知道,当汽车起步时受到的阻力越大(比如由自身重力或地面摩擦力引起等),或当我们提供给它的动力越小时,汽车起步就会越慢。其实晶振起振慢和汽车起步慢是一个道理: 无源晶振的起振时间在很大程度上依赖于晶振的特性和电路布局。在施加正常的激励功率之下,串行等效电阻(ESR)过大和外围电…

关于晶振起振时间太慢原因分析及解决方案

2022-07-15(无源晶振电路) 我们都知道,当汽车起步时受到的阻力越大(比如由自身重力或地面摩擦力引起等),或当我们提供给它的动力越小时,汽车起步就会越慢。其实晶振起振慢和汽车起步慢是一个道理: 无源晶振的起振时间在很大程度上依赖于晶振的特性和电路布局。在施加正常的激励功率之下,串行等效电阻(ESR)过大和外围电… -

; ) 无源晶振的PIN1脚可以接地吗?

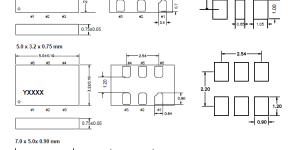

2022-07-14无源晶振的PIN1脚可以接地吗? 答:一般情况下不可以。 无源晶振PIN1与PIN3脚为频率输入脚和频率输出脚,这两个脚没有方向性,也没有正负极之分,因此接入电路时,焊接反了没关系。无源晶振PIN2与PIN4脚与晶振金属外壳连接,为接地脚。 必须提醒的是,在皮尔斯振荡电路中一旦PIN1…

无源晶振的PIN1脚可以接地吗?

2022-07-14无源晶振的PIN1脚可以接地吗? 答:一般情况下不可以。 无源晶振PIN1与PIN3脚为频率输入脚和频率输出脚,这两个脚没有方向性,也没有正负极之分,因此接入电路时,焊接反了没关系。无源晶振PIN2与PIN4脚与晶振金属外壳连接,为接地脚。 必须提醒的是,在皮尔斯振荡电路中一旦PIN1… -

; ) 无源晶振与CPU连接图及分频电路图解

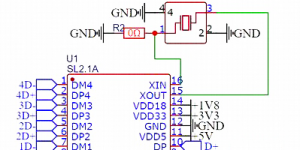

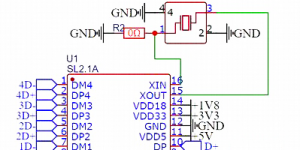

2022-07-13(无源晶振与CPU连接图) CPU需要复杂的时序电路完成不同的指令功能。一般时钟信号可以由两种信号产生:一种是内部方式,利用芯片内部的振荡电路,产生时钟信号;另一种为外部方式,时钟信号由外部引入,时钟晶振就是芯片的外部时钟信号源。 (分频电路图解) 时钟晶振的主要作用是通过分频电路向显…

无源晶振与CPU连接图及分频电路图解

2022-07-13(无源晶振与CPU连接图) CPU需要复杂的时序电路完成不同的指令功能。一般时钟信号可以由两种信号产生:一种是内部方式,利用芯片内部的振荡电路,产生时钟信号;另一种为外部方式,时钟信号由外部引入,时钟晶振就是芯片的外部时钟信号源。 (分频电路图解) 时钟晶振的主要作用是通过分频电路向显… -

; ) 晶振Buffer:一颗晶振为多个芯片提供时钟参考

2022-07-11一颗晶振能为多个芯片同时提供参考时钟信号吗? 举例:在某款控制主板上有CPU、CPLD、网络处理ASIC、时钟发生器等多颗芯片,都需要25MHz的参考时钟信号,可以选择的方案有: 方案1: 选择一颗晶振同时为几个芯片提供参考,这种方案很大的弊端是时钟信号完整性问题(如晶诺威科技产常规有源晶振的负载为…

晶振Buffer:一颗晶振为多个芯片提供时钟参考

2022-07-11一颗晶振能为多个芯片同时提供参考时钟信号吗? 举例:在某款控制主板上有CPU、CPLD、网络处理ASIC、时钟发生器等多颗芯片,都需要25MHz的参考时钟信号,可以选择的方案有: 方案1: 选择一颗晶振同时为几个芯片提供参考,这种方案很大的弊端是时钟信号完整性问题(如晶诺威科技产常规有源晶振的负载为… -

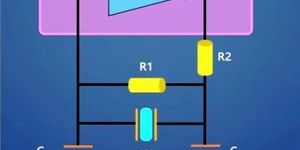

; ) 数字电路中的VCC,VDD和VSS分别指的是什么?

2022-07-11对于数字电路来说,VCC是电路的供电电压,VDD是芯片的工作电压(通常Vcc>Vdd)。有些IC既有VDD引脚又有VCC引脚,说明这种器件自身带有电压转换功能。VSS是接地点。 VCC:C=circuit 表示电路的意思, 即接入电路的电压 VDD:D=device 表示器件的意思, 即器件内…

数字电路中的VCC,VDD和VSS分别指的是什么?

2022-07-11对于数字电路来说,VCC是电路的供电电压,VDD是芯片的工作电压(通常Vcc>Vdd)。有些IC既有VDD引脚又有VCC引脚,说明这种器件自身带有电压转换功能。VSS是接地点。 VCC:C=circuit 表示电路的意思, 即接入电路的电压 VDD:D=device 表示器件的意思, 即器件内… -

; ) 差分信号线中间可否加地线?

2022-07-10差分信号中间一般是不能加地线。因为差分信号的应用原理最重要的一点便是利用差分信号间相互耦合(coupling)所带来的好处,如flux cancellation,抗噪声(noise immunity)能力等。若在中间加地线,便会破坏耦合效应。 附:MEMS差分振荡器SiT9121主要参数: 频率范围…

差分信号线中间可否加地线?

2022-07-10差分信号中间一般是不能加地线。因为差分信号的应用原理最重要的一点便是利用差分信号间相互耦合(coupling)所带来的好处,如flux cancellation,抗噪声(noise immunity)能力等。若在中间加地线,便会破坏耦合效应。 附:MEMS差分振荡器SiT9121主要参数: 频率范围… -

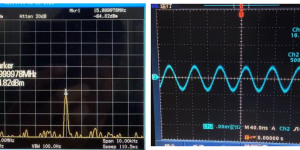

; ) 如何抑止电磁辐射对时钟信号的干扰?

2022-07-09如果在EMC测试中发现时钟信号的谐波超标严重,在PCB设计中该如何抑止电磁辐射呢? 首先,EMC的三要素为辐射源,传播途径和受害体。而传播途径分为空间辐射传播和电缆传导。所以,要抑制谐波,首先看看它传播的途径。电源去耦(在电源引脚上连接去耦电容)是解决传导方式传播,此外,也要考虑必要的匹配和屏蔽。 …

如何抑止电磁辐射对时钟信号的干扰?

2022-07-09如果在EMC测试中发现时钟信号的谐波超标严重,在PCB设计中该如何抑止电磁辐射呢? 首先,EMC的三要素为辐射源,传播途径和受害体。而传播途径分为空间辐射传播和电缆传导。所以,要抑制谐波,首先看看它传播的途径。电源去耦(在电源引脚上连接去耦电容)是解决传导方式传播,此外,也要考虑必要的匹配和屏蔽。 … -

; ) PCBA如何避免高频信号干扰?

2022-07-08PCBA如何避免高频信号干扰? 在PCBA上,避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。 为避免高频干扰,晶诺威科技建议方法如下: 1、拉大高速信号和模拟信号之间的距离 2、增加groundguard/shunttraces在模拟信号旁边 3、注意…

PCBA如何避免高频信号干扰?

2022-07-08PCBA如何避免高频信号干扰? 在PCBA上,避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。 为避免高频干扰,晶诺威科技建议方法如下: 1、拉大高速信号和模拟信号之间的距离 2、增加groundguard/shunttraces在模拟信号旁边 3、注意… -

; ) 如何检测PCB是否达到了设计要求?

2022-07-07很多PCB厂家在PCB加工完成出厂前,都要经过加电的网络通断测试,以确保所有连线正确。同时,越来越多的厂家也采用X光测试,检查焊接、蚀刻或层压时的一些可能性故障。 对于贴片加工后的成品板,一般采用ICT测试检查,这需要在PCB设计时添加ICT测试点。如果出现问题,也可以通过一种特殊的X光检查设备排除…

如何检测PCB是否达到了设计要求?

2022-07-07很多PCB厂家在PCB加工完成出厂前,都要经过加电的网络通断测试,以确保所有连线正确。同时,越来越多的厂家也采用X光测试,检查焊接、蚀刻或层压时的一些可能性故障。 对于贴片加工后的成品板,一般采用ICT测试检查,这需要在PCB设计时添加ICT测试点。如果出现问题,也可以通过一种特殊的X光检查设备排除… -

; ) 如何使用示波器测试晶振是否起振?

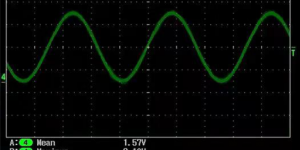

2022-07-06如何使用示波器验证晶振已经起振? 1、针对有些⽰波器,如果探头不打到衰减档可能会引起晶振停振,因此请首先将探头调至衰减档10X档位。 2、给电路板正常上电。 3、⽤⽰波器探头连接晶振两个管脚中任意⼀个引脚与地线。 4、如果⽆源晶振已经起振,当示波器探头测试晶振两个管脚时,即可以观测到振荡波形且频率与…

如何使用示波器测试晶振是否起振?

2022-07-06如何使用示波器验证晶振已经起振? 1、针对有些⽰波器,如果探头不打到衰减档可能会引起晶振停振,因此请首先将探头调至衰减档10X档位。 2、给电路板正常上电。 3、⽤⽰波器探头连接晶振两个管脚中任意⼀个引脚与地线。 4、如果⽆源晶振已经起振,当示波器探头测试晶振两个管脚时,即可以观测到振荡波形且频率与…