-

; ) 如何满足石英晶体振荡器的振荡条件?

2022-07-04石英晶体振荡器的振幅条件是振荡起动及能正常持续振荡的条件,回路上的负性电阻绝对值│-R│。 负性电阻 |- R| = Rtest + Re Rtest=与晶振串联连接纯电阻 Re=振荡时的有效电阻=R1(1+C0/CL)^2 建议振荡宽限为晶振等效串联电阻RR的5倍之上:│-R│≥ 5RR;电路进入…

如何满足石英晶体振荡器的振荡条件?

2022-07-04石英晶体振荡器的振幅条件是振荡起动及能正常持续振荡的条件,回路上的负性电阻绝对值│-R│。 负性电阻 |- R| = Rtest + Re Rtest=与晶振串联连接纯电阻 Re=振荡时的有效电阻=R1(1+C0/CL)^2 建议振荡宽限为晶振等效串联电阻RR的5倍之上:│-R│≥ 5RR;电路进入… -

; ) 晶片破损及电阻值变异引发晶振停振问题分析

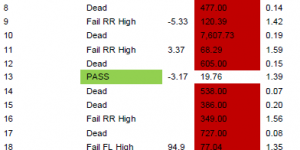

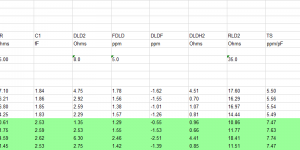

2022-07-02晶片破损及电阻值变异引发晶振停振问题分析如下: 不良晶振为49S与圆柱体晶振,安装方式为手工焊接。不良品在我司S&A 250B上测试,数据如下: 数据组1 数据组2 数据组3 数据组4 排除误判以外,分析如下: 1、针对测试数据组1~3及晶振49S不良品开壳观测,发现晶片出现裂…

晶片破损及电阻值变异引发晶振停振问题分析

2022-07-02晶片破损及电阻值变异引发晶振停振问题分析如下: 不良晶振为49S与圆柱体晶振,安装方式为手工焊接。不良品在我司S&A 250B上测试,数据如下: 数据组1 数据组2 数据组3 数据组4 排除误判以外,分析如下: 1、针对测试数据组1~3及晶振49S不良品开壳观测,发现晶片出现裂… -

; ) 关于针对晶振进行防静电保护的重要性

2022-07-01什么是静电放电(英文 ESD - Electrostatic Discharge)? ESD(“静电放电”)是由电绝缘材料中的大电位差引起的火花或击穿,从而产生非常短的高电流脉冲。 物体的静电荷是由不同材料的摩擦电引起的。放电会损坏敏感的电子元件。例如,穿着绝缘性能良好的鞋子在绝缘性能良好的地板上移…

关于针对晶振进行防静电保护的重要性

2022-07-01什么是静电放电(英文 ESD - Electrostatic Discharge)? ESD(“静电放电”)是由电绝缘材料中的大电位差引起的火花或击穿,从而产生非常短的高电流脉冲。 物体的静电荷是由不同材料的摩擦电引起的。放电会损坏敏感的电子元件。例如,穿着绝缘性能良好的鞋子在绝缘性能良好的地板上移… -

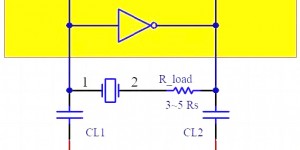

; ) 无源晶振起振电路设计:C0/C1,CL及RR说明

2022-07-01无源晶振起振电路设计:关于C0/C1, CL及RR说明如下: C0/C1对晶体稳定性的影响 晶体(无源晶振)的静态电容C0和动态电容C1大小,与晶片电极面积大小(体积大小)成正比,不同厂家设计C0也有差异。 同一频率C0/C1的不同会影响振荡电路的稳定性: C0/C1大,频率上升到标称频率前电抗变大…

无源晶振起振电路设计:C0/C1,CL及RR说明

2022-07-01无源晶振起振电路设计:关于C0/C1, CL及RR说明如下: C0/C1对晶体稳定性的影响 晶体(无源晶振)的静态电容C0和动态电容C1大小,与晶片电极面积大小(体积大小)成正比,不同厂家设计C0也有差异。 同一频率C0/C1的不同会影响振荡电路的稳定性: C0/C1大,频率上升到标称频率前电抗变大… -

; ) 有源晶振脚1输出:三态Tri-state,使能OE,E/D及待机ST解释

2022-07-01关于有源晶振三态Tri-state,使能OE, E/D及待机ST的知识,晶诺威科技解释如下: 有源晶振(石英晶体振荡器)的脚1(又被称之为1号脚或pin#1)通常是Output Enable(OE)或者Enable/Disable (E/D)。也会叫做Stand-by (ST), Power Dow…

有源晶振脚1输出:三态Tri-state,使能OE,E/D及待机ST解释

2022-07-01关于有源晶振三态Tri-state,使能OE, E/D及待机ST的知识,晶诺威科技解释如下: 有源晶振(石英晶体振荡器)的脚1(又被称之为1号脚或pin#1)通常是Output Enable(OE)或者Enable/Disable (E/D)。也会叫做Stand-by (ST), Power Dow… -

; ) 晶振功耗,晶振起振时间与晶振相噪

2022-07-01我们在追求晶振输出频率高精度及高稳定性的同时,也对其功耗、起振时间及相噪等三方面提出了更高要求。 显而易见,当前智能化电子产品呈现高精密化及网络通信设备呈现数据高速化等趋势。具备小尺寸和低功耗的晶振适合在移动设备和穿戴设备中使用,而该类电子产品的特点为:电源电压、电流、体积、功耗相应减小、驱动能力变…

晶振功耗,晶振起振时间与晶振相噪

2022-07-01我们在追求晶振输出频率高精度及高稳定性的同时,也对其功耗、起振时间及相噪等三方面提出了更高要求。 显而易见,当前智能化电子产品呈现高精密化及网络通信设备呈现数据高速化等趋势。具备小尺寸和低功耗的晶振适合在移动设备和穿戴设备中使用,而该类电子产品的特点为:电源电压、电流、体积、功耗相应减小、驱动能力变… -

; ) 针对晶振单体进行温测的重要性

2022-06-28工作环境的温度变化对晶振有两个方面的直接影响,一是频率,二是电阻。这两个参数都是晶振的关键电气参数。 首先,晶振都有“温漂”现象,这是石英晶体本身的物理特性所决定。晶振工厂主要是通过改变石英晶片切型方式及后期对石英晶片的再加工技术,来尽可能降低“温漂”对晶振频率的影响。晶振的应用基本原理是,其实际输…

针对晶振单体进行温测的重要性

2022-06-28工作环境的温度变化对晶振有两个方面的直接影响,一是频率,二是电阻。这两个参数都是晶振的关键电气参数。 首先,晶振都有“温漂”现象,这是石英晶体本身的物理特性所决定。晶振工厂主要是通过改变石英晶片切型方式及后期对石英晶片的再加工技术,来尽可能降低“温漂”对晶振频率的影响。晶振的应用基本原理是,其实际输… -

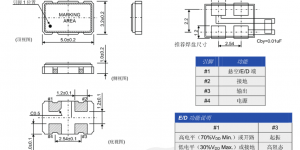

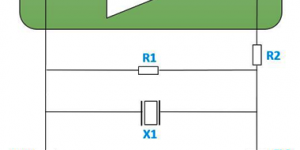

; ) 晶诺威科技晶振单体及上板上电测试电路匹配范例

2022-06-27晶诺威科技晶振单体及上板上电测试电路匹配范例,具体步骤如下: 举例:假设电路中晶振名称:X1 X1晶振电气参数:无源贴片晶振SMD3225-4pin, 16MHz, ±10PPM, CL=12pF, ECR<40Ω 测试环境及设备: 环境: 在室温25°C±3°C 和湿度 50 ~70% Rh…

晶诺威科技晶振单体及上板上电测试电路匹配范例

2022-06-27晶诺威科技晶振单体及上板上电测试电路匹配范例,具体步骤如下: 举例:假设电路中晶振名称:X1 X1晶振电气参数:无源贴片晶振SMD3225-4pin, 16MHz, ±10PPM, CL=12pF, ECR<40Ω 测试环境及设备: 环境: 在室温25°C±3°C 和湿度 50 ~70% Rh… -

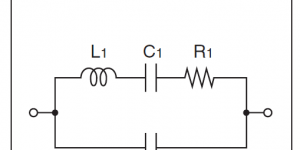

; ) 无源晶振主要电气参数及其对电路的影响

2022-06-27(无源晶振主要电气参数及其对电路的影响) RR 阻抗RR越小,晶振越容易起振;反之,若晶振ESR过高,则晶振不易起振,可能会给电路造成不稳定。 C1 动态电容 L1 动态电感 C0 静电容 静电容C0不能太高,否则易产生较大的副波,影响晶振频率稳定性。 FL 在特定负载电容以及激励功率下,频偏越小越…

无源晶振主要电气参数及其对电路的影响

2022-06-27(无源晶振主要电气参数及其对电路的影响) RR 阻抗RR越小,晶振越容易起振;反之,若晶振ESR过高,则晶振不易起振,可能会给电路造成不稳定。 C1 动态电容 L1 动态电感 C0 静电容 静电容C0不能太高,否则易产生较大的副波,影响晶振频率稳定性。 FL 在特定负载电容以及激励功率下,频偏越小越… -

; ) 8MHz晶振不良造成触摸屏失效问题解析

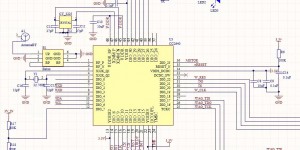

2022-06-228MHz晶振不良造成触摸屏失效问题解析如下: 不良表述:触摸屏失灵 拆机检查,目测没有发现存在脱焊或虚焊现象,换用一块新触摸主板后故障消失。故障排除步骤如下: 1、测故障主板上U27(DE21C)5V转3.3V正常 2、测单芯片STM32、24、36、48脚3.3V供电正常 3、红外接收管3.1V供…

8MHz晶振不良造成触摸屏失效问题解析

2022-06-228MHz晶振不良造成触摸屏失效问题解析如下: 不良表述:触摸屏失灵 拆机检查,目测没有发现存在脱焊或虚焊现象,换用一块新触摸主板后故障消失。故障排除步骤如下: 1、测故障主板上U27(DE21C)5V转3.3V正常 2、测单芯片STM32、24、36、48脚3.3V供电正常 3、红外接收管3.1V供…