-

; ) 负载电容CL选择错误导致32.768KHz晶振时间不准或停振

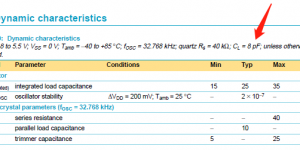

2022-06-13如上图所示,在某一款芯片对晶振32.768KHz规格要求中,晶振主要电气参数如下: 标称频率Nominal Frequency: 32.768KHz 负载电容CL: 8PF 等效电阻ESR:40KΩ 工作温度范围Operating Temperature Range:-40~+85℃ 频率稳定度Fr…

负载电容CL选择错误导致32.768KHz晶振时间不准或停振

2022-06-13如上图所示,在某一款芯片对晶振32.768KHz规格要求中,晶振主要电气参数如下: 标称频率Nominal Frequency: 32.768KHz 负载电容CL: 8PF 等效电阻ESR:40KΩ 工作温度范围Operating Temperature Range:-40~+85℃ 频率稳定度Fr… -

; ) 无源晶振的负载电容Load Capacitance与频偏Frequency Deviation

2022-06-10在无源晶振(石英晶体谐振器)电路应用中,我们期望获得稳定且精准的时钟信号,这取决于晶振的实际输出频率需要靠近中心频率。一般情况下,时钟信号的精准度及稳定度则主要由无源晶振本身精度及合适的外接电容所决定。 在做电路设计的时候,很多工程师不知道无源晶振的负载电容如何计算。在设计的时候,很多人都凭借的经验…

无源晶振的负载电容Load Capacitance与频偏Frequency Deviation

2022-06-10在无源晶振(石英晶体谐振器)电路应用中,我们期望获得稳定且精准的时钟信号,这取决于晶振的实际输出频率需要靠近中心频率。一般情况下,时钟信号的精准度及稳定度则主要由无源晶振本身精度及合适的外接电容所决定。 在做电路设计的时候,很多工程师不知道无源晶振的负载电容如何计算。在设计的时候,很多人都凭借的经验… -

; ) 如何通过晶振手册看晶振频率及负载电容?

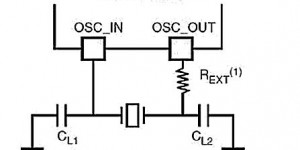

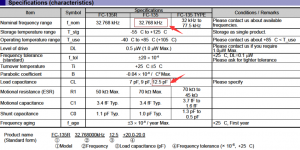

2022-06-06举例,某晶振手册如下: 通过上图晶振手册,我们可以看出晶振频率就是标称32.768KHz。若选取晶振负载CL(load capacitance)=12.5PF,负载电容大体可以按下面的计算,其中C1、C2取值要使得最终CL满足晶振手册中的12.5pF。例如C1、C2可取15pF~22pF左右。 关于…

如何通过晶振手册看晶振频率及负载电容?

2022-06-06举例,某晶振手册如下: 通过上图晶振手册,我们可以看出晶振频率就是标称32.768KHz。若选取晶振负载CL(load capacitance)=12.5PF,负载电容大体可以按下面的计算,其中C1、C2取值要使得最终CL满足晶振手册中的12.5pF。例如C1、C2可取15pF~22pF左右。 关于… -

; ) 为什么对于数码音频来说时钟信号如此重要?

2022-06-06凡是数字电路必须有时钟的,而时钟则是由高精度石英晶振提供。时钟信号可以比喻为像“心跳”一样为数字电路的各个部分的同步协调工作提供正确的时序参考。如果说DAC芯片(DAC英文全称:Digital to Analog Converter,数字—模拟转换器,它是将手机、电脑、CD唱片里存储的音乐文件,通过…

为什么对于数码音频来说时钟信号如此重要?

2022-06-06凡是数字电路必须有时钟的,而时钟则是由高精度石英晶振提供。时钟信号可以比喻为像“心跳”一样为数字电路的各个部分的同步协调工作提供正确的时序参考。如果说DAC芯片(DAC英文全称:Digital to Analog Converter,数字—模拟转换器,它是将手机、电脑、CD唱片里存储的音乐文件,通过… -

; ) 时钟信号对数字音频质量的影响

2022-06-05(理想时钟与实际时钟) 为系统中的每个设备传递标准的时钟信号是保证数字音频质量的重要步骤,因为时钟振荡器的不同,每个设备的时钟信号都会有一定量的偏差,这种偏差就会导致数字信号不精确,从而影响到音频的质量。 时钟恶化通常来源于抖动,在数字传输系统中,抖动被定义为数字信号的重要时刻在时间上偏离其理想位置…

时钟信号对数字音频质量的影响

2022-06-05(理想时钟与实际时钟) 为系统中的每个设备传递标准的时钟信号是保证数字音频质量的重要步骤,因为时钟振荡器的不同,每个设备的时钟信号都会有一定量的偏差,这种偏差就会导致数字信号不精确,从而影响到音频的质量。 时钟恶化通常来源于抖动,在数字传输系统中,抖动被定义为数字信号的重要时刻在时间上偏离其理想位置… -

; ) 晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

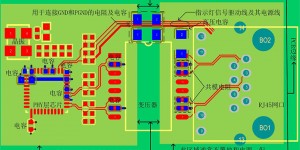

2022-05-31(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因…

晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

2022-05-31(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因… -

; ) 关于无源晶振振荡回路设计的四个注意事项

2022-05-30关于无源晶振振荡回路设计的四个注意事项,归纳如下: 1、晶振振荡回路参数设置参考 2、晶振振荡补偿 除非在振荡电路中提供足够的负极电阻(负性阻抗/负电阻/-R),否则会增加振荡启动时间,或不发生振荡。为避免该情况发生,请在电路设计时提供足够的负极电阻。 3、晶振负载电容 如果振荡电路中…

关于无源晶振振荡回路设计的四个注意事项

2022-05-30关于无源晶振振荡回路设计的四个注意事项,归纳如下: 1、晶振振荡回路参数设置参考 2、晶振振荡补偿 除非在振荡电路中提供足够的负极电阻(负性阻抗/负电阻/-R),否则会增加振荡启动时间,或不发生振荡。为避免该情况发生,请在电路设计时提供足够的负极电阻。 3、晶振负载电容 如果振荡电路中… -

; ) 有源晶振和无源晶振电路差异及应用注意事项

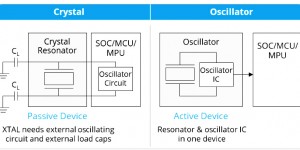

2022-05-19关于有源晶振和无源晶振电路差异,晶诺威科技解释如下: 有源晶振不需要匹配电容起振便可直接工作,从逻辑上讲,直接上电即可起振; 无源晶振需要在起振电路中匹配合适的电容(启动电容)才能正常起振。在起振电路中,在没有外接匹配电容的情况下,无源晶振也可以起振,但容易发生频偏超差问题,主要体现为“偏正”。 晶…

有源晶振和无源晶振电路差异及应用注意事项

2022-05-19关于有源晶振和无源晶振电路差异,晶诺威科技解释如下: 有源晶振不需要匹配电容起振便可直接工作,从逻辑上讲,直接上电即可起振; 无源晶振需要在起振电路中匹配合适的电容(启动电容)才能正常起振。在起振电路中,在没有外接匹配电容的情况下,无源晶振也可以起振,但容易发生频偏超差问题,主要体现为“偏正”。 晶… -

; ) 如何减少电路板寄生电容对贴片晶振的影响?

2022-05-18如何减少电路板寄生电容对贴片晶振的影响? 措施:针对多层板,建议挖空晶振下方的平面层。 原因分析: 如果贴片晶振焊盘下方存在寄生电容过大,则会直接导致晶振频偏或输出频率不稳定,引发电子设备功能性不良。 在常温之下。PCB板工作时可能不会出现问题,但是在一些高低温的条件下,寄生电容就会增加或不稳定,这…

如何减少电路板寄生电容对贴片晶振的影响?

2022-05-18如何减少电路板寄生电容对贴片晶振的影响? 措施:针对多层板,建议挖空晶振下方的平面层。 原因分析: 如果贴片晶振焊盘下方存在寄生电容过大,则会直接导致晶振频偏或输出频率不稳定,引发电子设备功能性不良。 在常温之下。PCB板工作时可能不会出现问题,但是在一些高低温的条件下,寄生电容就会增加或不稳定,这… -

; ) DLD2不良导致晶振休眠原因分析

2022-05-17关于DLD2不良导致晶振休眠原因,分析如下: DLD2 英文为Drive Level Dependency。为在不同的功率驱动晶振时,所得之最大阻抗与最小阻抗之差。 DLD2越小越好,当晶振制程受污染时,则DLD2值会偏高,导致时振与时不振现象,即 “晶振休眠”。好的晶振不会因驱动功率变化而产生较高…

DLD2不良导致晶振休眠原因分析

2022-05-17关于DLD2不良导致晶振休眠原因,分析如下: DLD2 英文为Drive Level Dependency。为在不同的功率驱动晶振时,所得之最大阻抗与最小阻抗之差。 DLD2越小越好,当晶振制程受污染时,则DLD2值会偏高,导致时振与时不振现象,即 “晶振休眠”。好的晶振不会因驱动功率变化而产生较高…