-

; ) RTC晶振32.768KHz时钟电路原理及振荡电路计算公式

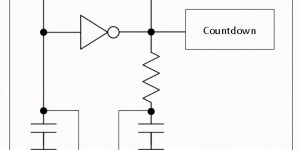

2021-08-24RTC晶振的频率会受到其外接电容的影响。皮尔斯振荡器是RTC内部最常用的RTC振荡器电路。它通常由RTC晶振,逆变器和外接电容组成。 (RTC内部装有一个振荡器电路) 由RTC晶振和外接电容组成的等效电路如下图所示 (基于RTC晶振和外接电容的等效电路) 在所示的电路中,RCL串联电路与C0和CL并…

RTC晶振32.768KHz时钟电路原理及振荡电路计算公式

2021-08-24RTC晶振的频率会受到其外接电容的影响。皮尔斯振荡器是RTC内部最常用的RTC振荡器电路。它通常由RTC晶振,逆变器和外接电容组成。 (RTC内部装有一个振荡器电路) 由RTC晶振和外接电容组成的等效电路如下图所示 (基于RTC晶振和外接电容的等效电路) 在所示的电路中,RCL串联电路与C0和CL并… -

; ) 在晶振应用中的时钟偏移(skew)和时钟抖动(jitter)分别指什么?

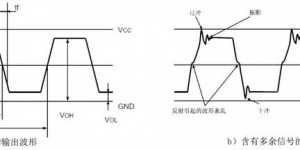

2021-08-22在晶振应用中的时钟偏移(skew)和时钟抖动 时钟偏移(skew) 指同样的时钟产生的多个子时钟信号之间的延时差异。skew通常是时钟相位上的不确定。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。完成布局布线后,物理路径延时是固定的,所以在设计中…

在晶振应用中的时钟偏移(skew)和时钟抖动(jitter)分别指什么?

2021-08-22在晶振应用中的时钟偏移(skew)和时钟抖动 时钟偏移(skew) 指同样的时钟产生的多个子时钟信号之间的延时差异。skew通常是时钟相位上的不确定。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。完成布局布线后,物理路径延时是固定的,所以在设计中… -

; ) 关于RTC实时时钟晶振32.768KHz电路设计

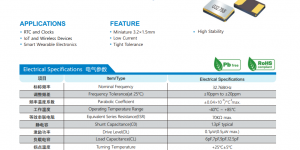

2021-08-21(RTC实时时钟贴片晶振32.768KHz:SMD3215/FC-135) SMD3215 32.768KHz 2脚电路设计 在很多数字集成电路中都要用到实时时钟( RTC, Real Time Clock ) , 而确保RTC工作计时正确的关键部分就是32.756KHz 的晶体振荡器电路。 电路结…

关于RTC实时时钟晶振32.768KHz电路设计

2021-08-21(RTC实时时钟贴片晶振32.768KHz:SMD3215/FC-135) SMD3215 32.768KHz 2脚电路设计 在很多数字集成电路中都要用到实时时钟( RTC, Real Time Clock ) , 而确保RTC工作计时正确的关键部分就是32.756KHz 的晶体振荡器电路。 电路结… -

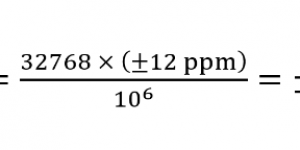

; ) 通过PPM计算MHz晶振频率偏差及32.768KHz晶振计时公式

2021-08-19PPM是英文Parts Per Million的缩写,表示百万分之几。换句话说:1PPM则代表百万分之一的误差。 举例:若一颗晶振为12.000000MHz,即:12000000Hz 精度为±30ppm,那么误差频率为:30/100万*12M=360Hz 精度为±20ppm,那么误差频率为:20/1…

通过PPM计算MHz晶振频率偏差及32.768KHz晶振计时公式

2021-08-19PPM是英文Parts Per Million的缩写,表示百万分之几。换句话说:1PPM则代表百万分之一的误差。 举例:若一颗晶振为12.000000MHz,即:12000000Hz 精度为±30ppm,那么误差频率为:30/100万*12M=360Hz 精度为±20ppm,那么误差频率为:20/1… -

; ) 为何外接电容越大晶振起振越慢?

2021-08-18首先说明的是:但凡需要外接电容的晶振均为无源晶振。另外,注意区分外接电容C1和C2(接地电容,对地电容)并不等同于晶振负载电容(CL)。C1和C2是电路板和包括IC 和晶振在内的组件的总电容值。 一般情况下,增大无源晶振的外接电容将会使晶振振荡频率下降,即偏负向。举例,若无源晶振12MHz的外接电容…

为何外接电容越大晶振起振越慢?

2021-08-18首先说明的是:但凡需要外接电容的晶振均为无源晶振。另外,注意区分外接电容C1和C2(接地电容,对地电容)并不等同于晶振负载电容(CL)。C1和C2是电路板和包括IC 和晶振在内的组件的总电容值。 一般情况下,增大无源晶振的外接电容将会使晶振振荡频率下降,即偏负向。举例,若无源晶振12MHz的外接电容… -

; ) 如何设计无源晶振及两颗外接电容在PCB的最佳位置?

2021-08-17无源晶振及两颗外接电容在PCB的位置 两颗外接电容应尽量靠近晶振引脚(频率输入脚与频率输出脚)设计。 晶振核心部件为石英晶体,容易受外力撞击或跌落影响而破碎。在PCB布线时最好不要把晶振设计在PCB边缘,尽量使其靠近芯片。 晶振走线需要用GND保护稳妥,远离敏感信号源,如RF及高速信号,以免频率信号…

如何设计无源晶振及两颗外接电容在PCB的最佳位置?

2021-08-17无源晶振及两颗外接电容在PCB的位置 两颗外接电容应尽量靠近晶振引脚(频率输入脚与频率输出脚)设计。 晶振核心部件为石英晶体,容易受外力撞击或跌落影响而破碎。在PCB布线时最好不要把晶振设计在PCB边缘,尽量使其靠近芯片。 晶振走线需要用GND保护稳妥,远离敏感信号源,如RF及高速信号,以免频率信号… -

; ) 晶振周围相噪phase noise源及相噪对策

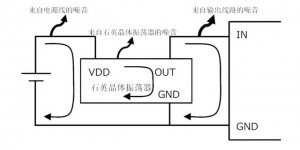

2021-08-13(石英晶体振荡器周围可产生相噪的电路) 相噪phase noise发生源分为主要三大类: (1)来自电源线的相噪:在晶振工作过程中,电源线中将产生脉动。电源线起到天线的作用脉动作为相噪释放。防止电源相噪时重要的是如何阻止或吸收晶振所产生的脉动流入电源线。为此而采取的对策可防止其它元器件所产生的外來相…

晶振周围相噪phase noise源及相噪对策

2021-08-13(石英晶体振荡器周围可产生相噪的电路) 相噪phase noise发生源分为主要三大类: (1)来自电源线的相噪:在晶振工作过程中,电源线中将产生脉动。电源线起到天线的作用脉动作为相噪释放。防止电源相噪时重要的是如何阻止或吸收晶振所产生的脉动流入电源线。为此而采取的对策可防止其它元器件所产生的外來相… -

; ) 如何控制晶振时钟信号的偏移skew?

2021-08-13晶振时钟信号偏移skew概念 整个芯片中时钟信号到达各级电路的时间差即为时钟偏移skew。 造成晶振时钟信号偏移skew的根本原因 短路径问题:即逻辑单元速度快,输出数据比时钟传播到下个逻辑单元还要快,就会造成数据丢失,从而导致逻辑功能出错。 如何控制晶振时钟信号的偏移skew?建议有以下五点: 添…

如何控制晶振时钟信号的偏移skew?

2021-08-13晶振时钟信号偏移skew概念 整个芯片中时钟信号到达各级电路的时间差即为时钟偏移skew。 造成晶振时钟信号偏移skew的根本原因 短路径问题:即逻辑单元速度快,输出数据比时钟传播到下个逻辑单元还要快,就会造成数据丢失,从而导致逻辑功能出错。 如何控制晶振时钟信号的偏移skew?建议有以下五点: 添… -

; ) 晶振低相噪low phase noise电路设计图

2021-08-12晶振低相噪low phase noise电路主要包括以下四个方面: 旁路电容器: 旁路电容器常用于除去相噪(noise)。它可以降低交流电源的阻抗使电路稳定工作,还可以吸电源线中的相噪。大多相噪问题可通过选择安装适宜常数的旁路电容器來解决。 旁路电容器容量: 通常使用的旁路电容器容量大致在0.01u…

晶振低相噪low phase noise电路设计图

2021-08-12晶振低相噪low phase noise电路主要包括以下四个方面: 旁路电容器: 旁路电容器常用于除去相噪(noise)。它可以降低交流电源的阻抗使电路稳定工作,还可以吸电源线中的相噪。大多相噪问题可通过选择安装适宜常数的旁路电容器來解决。 旁路电容器容量: 通常使用的旁路电容器容量大致在0.01u… -

; ) 关于有源晶振频率偏差问题的解决方案

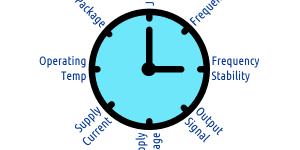

2021-08-12一般情况下,若选对所需精度的有源晶振,在实际工作中,有源晶振发生频偏问题很少见。 现归纳导致有源晶振频率偏差的主要因素如下: 1、 环境温度超出有源晶振规定工作温度范围。 解决方案:更换晶振,选择宽温有源晶振,如:把工作温度-20℃~+70℃改为-40℃~+85℃晶振产品。 2、电源变化可能导致有源…

关于有源晶振频率偏差问题的解决方案

2021-08-12一般情况下,若选对所需精度的有源晶振,在实际工作中,有源晶振发生频偏问题很少见。 现归纳导致有源晶振频率偏差的主要因素如下: 1、 环境温度超出有源晶振规定工作温度范围。 解决方案:更换晶振,选择宽温有源晶振,如:把工作温度-20℃~+70℃改为-40℃~+85℃晶振产品。 2、电源变化可能导致有源…