-

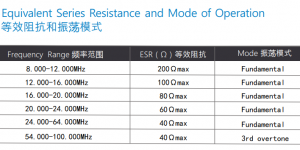

; ) 什么是晶振的等效串联阻抗 ( Equivalent Series Resistance ,ESR)

2021-11-02(ESR for Crystal SMD3225 series) The ESR of a crystal is the resistance exhibited at series resonance, it is proportional to the power dissipated with…

什么是晶振的等效串联阻抗 ( Equivalent Series Resistance ,ESR)

2021-11-02(ESR for Crystal SMD3225 series) The ESR of a crystal is the resistance exhibited at series resonance, it is proportional to the power dissipated with… -

; ) 晶振本身无异常却不起振怎么办?

2021-11-02这种情况常见于无源晶振应用,尤其是32.768KHz晶振。首先建议把该晶振交由晶振供应商,针对晶振主要电气参数通过专业测试仪测试,如250B或350D。在确定晶振各项电气参数完全符合指标(如DLD2及负载电容等)之后,即,100%确认晶振单体无异常,再转向晶振的实际应用方向。 晶振本身无异常却不起振…

晶振本身无异常却不起振怎么办?

2021-11-02这种情况常见于无源晶振应用,尤其是32.768KHz晶振。首先建议把该晶振交由晶振供应商,针对晶振主要电气参数通过专业测试仪测试,如250B或350D。在确定晶振各项电气参数完全符合指标(如DLD2及负载电容等)之后,即,100%确认晶振单体无异常,再转向晶振的实际应用方向。 晶振本身无异常却不起振… -

; ) 如何判断32.768KHz晶振的好坏

2021-10-29表晶32.768kHz贴片晶振是市面上使用最为广泛的一类晶振。 爱普生(EPSON)/精工(SEIKO)目前提供三类32.768KHz贴片晶振产品以满足客户不同需要,分别是:32.768kHz有源贴片晶振(OSC),32.768KHz无源贴片晶振(X'tal)和内置32.768KHz晶体谐振器的实时…

如何判断32.768KHz晶振的好坏

2021-10-29表晶32.768kHz贴片晶振是市面上使用最为广泛的一类晶振。 爱普生(EPSON)/精工(SEIKO)目前提供三类32.768KHz贴片晶振产品以满足客户不同需要,分别是:32.768kHz有源贴片晶振(OSC),32.768KHz无源贴片晶振(X'tal)和内置32.768KHz晶体谐振器的实时… -

; ) 无源晶振起振条件:振幅起振条件与相位起振条件

2021-10-29在晶振电路中,当环路增益大于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号相比于原来的信号在幅度上要大。这时振荡回路中的信号经过反复反馈放大后,不断增大,最终驱动晶体振荡。 起振条件也有两层意思: 1、振幅起振条件: 振幅跟振动回路有关,主要由IC电压决定。 表示输出信号振幅大于输入…

无源晶振起振条件:振幅起振条件与相位起振条件

2021-10-29在晶振电路中,当环路增益大于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号相比于原来的信号在幅度上要大。这时振荡回路中的信号经过反复反馈放大后,不断增大,最终驱动晶体振荡。 起振条件也有两层意思: 1、振幅起振条件: 振幅跟振动回路有关,主要由IC电压决定。 表示输出信号振幅大于输入… -

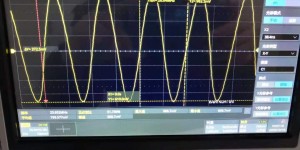

; ) 关于无源晶振驱动电流功率drive level说明及测试方法

2021-10-28无源晶振的驱动电流drive level 晶振驱动电流表示振荡电路工作时无源晶振的功耗驱动级别,驱动功率(激励功率)单位为μw,这个数值可以参照晶振规格书。说明一下:晶振产品的驱动电流已由晶振制造商决定。无源晶振保持在规范内驱动级别非常关键。过高的驱动电流可能会导致频率和等效串联电阻的意外变化。 英…

关于无源晶振驱动电流功率drive level说明及测试方法

2021-10-28无源晶振的驱动电流drive level 晶振驱动电流表示振荡电路工作时无源晶振的功耗驱动级别,驱动功率(激励功率)单位为μw,这个数值可以参照晶振规格书。说明一下:晶振产品的驱动电流已由晶振制造商决定。无源晶振保持在规范内驱动级别非常关键。过高的驱动电流可能会导致频率和等效串联电阻的意外变化。 英… -

; ) 蓝牙+WIFI双频模块专用晶振37.4MHz规格参数

2021-10-26WiFi模块:实现互联网与电子终端之间的无线数据传输 蓝牙(bluetooth)模块:实现近距离电子终端之间数据传输 晶诺威科技生产的蓝牙+WIFI双频模块专用晶振37.4MHz规格参数介绍如下: 蓝牙模块(bluetooth)是集成蓝牙功能的PCBA,应用于短距离无线数据通信,而WiFi模式,TT…

蓝牙+WIFI双频模块专用晶振37.4MHz规格参数

2021-10-26WiFi模块:实现互联网与电子终端之间的无线数据传输 蓝牙(bluetooth)模块:实现近距离电子终端之间数据传输 晶诺威科技生产的蓝牙+WIFI双频模块专用晶振37.4MHz规格参数介绍如下: 蓝牙模块(bluetooth)是集成蓝牙功能的PCBA,应用于短距离无线数据通信,而WiFi模式,TT… -

; ) Oscillator是无源晶振还是有源晶振?

2021-10-26Oscillator是无源晶振还是有源晶振? 答:Oscillator是有源晶振。 在电子学上,通常将含有晶体管元件的电路称作“有源电路”(如有源音箱、有源滤波器等),而仅由阻容元件组成的电路称作“无源电路”。电脑中的晶体振荡器也分为无源晶振和有源晶振两种类型。无源晶振与有源晶振的英文名称不同,无源…

Oscillator是无源晶振还是有源晶振?

2021-10-26Oscillator是无源晶振还是有源晶振? 答:Oscillator是有源晶振。 在电子学上,通常将含有晶体管元件的电路称作“有源电路”(如有源音箱、有源滤波器等),而仅由阻容元件组成的电路称作“无源电路”。电脑中的晶体振荡器也分为无源晶振和有源晶振两种类型。无源晶振与有源晶振的英文名称不同,无源… -

; ) 晶振电路的平衡条件:振幅平衡与相位平衡

2021-10-25在晶振电路中,当环路增益等于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号和原来的信号一模一样,这时振荡器才有持续的稳定的振荡信号输出,振荡回路达到平衡状态。从另一个角度来分析,可以认为,即使没有输入信号,回路也有输出。 平衡条件有两层意思: 1、振幅平衡条件 表示输入输出的幅度一致…

晶振电路的平衡条件:振幅平衡与相位平衡

2021-10-25在晶振电路中,当环路增益等于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号和原来的信号一模一样,这时振荡器才有持续的稳定的振荡信号输出,振荡回路达到平衡状态。从另一个角度来分析,可以认为,即使没有输入信号,回路也有输出。 平衡条件有两层意思: 1、振幅平衡条件 表示输入输出的幅度一致… -

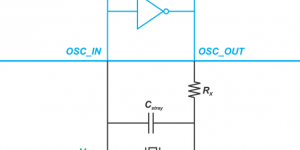

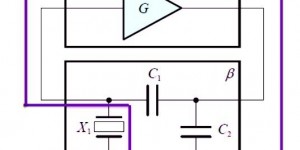

; ) 晶振Pierce电路与Colpitts电路对比

2021-10-23不同于大多数芯片方案常用的Pierce电路,Colpitts电路也是电容三点式晶振电路的一种。实际上,Pierce电路衍生于Colpitts电路。Colpitts电路的驱动能力很弱,一般负阻只有200欧姆左右,而Pierce电路的驱动能力很强,一般负阻有10K左右。所以,Colpitts电路在做晶振…

晶振Pierce电路与Colpitts电路对比

2021-10-23不同于大多数芯片方案常用的Pierce电路,Colpitts电路也是电容三点式晶振电路的一种。实际上,Pierce电路衍生于Colpitts电路。Colpitts电路的驱动能力很弱,一般负阻只有200欧姆左右,而Pierce电路的驱动能力很强,一般负阻有10K左右。所以,Colpitts电路在做晶振… -

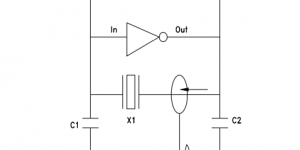

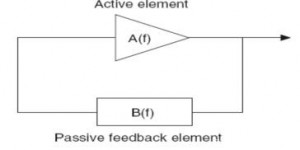

; ) 晶振电路:振荡电路放大器及环路闭环增益

2021-10-22关于晶振电路中的振荡电路,可以理解为一种能量转换装置,它的能量来源一般是直流供电电源,经过振荡电路转换以后,直流能量转换为一种一定频率、一定幅度、一定波形的交流能量输出。直流电源只是提供电路能够正常工作的静态电流,并不是输入信号。振荡电路在没有输入信号的情况下,能够自行产生一定周期性的交流信号。 晶…

晶振电路:振荡电路放大器及环路闭环增益

2021-10-22关于晶振电路中的振荡电路,可以理解为一种能量转换装置,它的能量来源一般是直流供电电源,经过振荡电路转换以后,直流能量转换为一种一定频率、一定幅度、一定波形的交流能量输出。直流电源只是提供电路能够正常工作的静态电流,并不是输入信号。振荡电路在没有输入信号的情况下,能够自行产生一定周期性的交流信号。 晶…