-

; ) 晶体振荡器时钟电路设计及振荡器方向识别

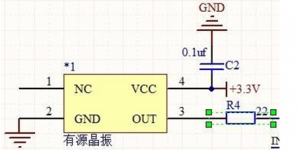

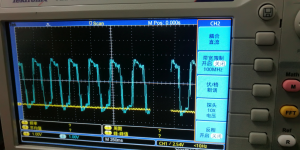

2020-11-12在晶体振荡器,即有源晶振,时钟电路设计及应用时,请注意以下六点: (常见晶体振荡器时钟电路设计图) 有个点标记的为1脚,按逆时针(管脚向下)分别为2、3、4。 晶体振荡器通常的用法:一脚悬空,二脚接地,三脚接信号输出,四脚接电压。注意不要贴反,否则很可能会烧坏有源晶振。 电源输入时,严…

晶体振荡器时钟电路设计及振荡器方向识别

2020-11-12在晶体振荡器,即有源晶振,时钟电路设计及应用时,请注意以下六点: (常见晶体振荡器时钟电路设计图) 有个点标记的为1脚,按逆时针(管脚向下)分别为2、3、4。 晶体振荡器通常的用法:一脚悬空,二脚接地,三脚接信号输出,四脚接电压。注意不要贴反,否则很可能会烧坏有源晶振。 电源输入时,严… -

; ) 晶振温漂是什么?如何通过晶振选型来解决温漂问题?

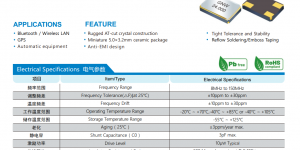

2020-11-11晶振在产品电路中的温漂大,就意味着频率偏差大,严重时会直接影响产品的功能及性能。因此在晶振电路设计及晶振选型时,特别需要重视晶振的温漂特性。作为晶振厂家,针对晶振温漂问题及解决方案,晶诺威科技解释如下: 晶振温漂:晶振频率随着外界温度变化而随之变化的现象就是温漂。 那么,晶振为何会出现温漂现象?石英…

晶振温漂是什么?如何通过晶振选型来解决温漂问题?

2020-11-11晶振在产品电路中的温漂大,就意味着频率偏差大,严重时会直接影响产品的功能及性能。因此在晶振电路设计及晶振选型时,特别需要重视晶振的温漂特性。作为晶振厂家,针对晶振温漂问题及解决方案,晶诺威科技解释如下: 晶振温漂:晶振频率随着外界温度变化而随之变化的现象就是温漂。 那么,晶振为何会出现温漂现象?石英… -

; ) 晶振导致时钟芯片不工作的常见原因及解决方案

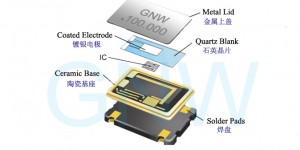

2020-11-11晶诺威科技归纳晶振导致时钟芯片不工作的常见原因及解决方案如下五点: 在晶振制造过程中压封的环节,晶振内部要求抽真空/充氮气,如果发生压封不良,即石英晶振的密封性不好时,在酒精加压的条件下,其表现为漏气,称之为双漏,也会导致晶振不振。 由于石英晶片本身的厚度很薄,当激励功率过大时,会使内部石英晶片破损…

晶振导致时钟芯片不工作的常见原因及解决方案

2020-11-11晶诺威科技归纳晶振导致时钟芯片不工作的常见原因及解决方案如下五点: 在晶振制造过程中压封的环节,晶振内部要求抽真空/充氮气,如果发生压封不良,即石英晶振的密封性不好时,在酒精加压的条件下,其表现为漏气,称之为双漏,也会导致晶振不振。 由于石英晶片本身的厚度很薄,当激励功率过大时,会使内部石英晶片破损… -

; ) 哪些晶振参数对振荡电路有较大影响?

2020-11-10基于晶振内部核心部件石英水晶片材质特性及生产工艺等诸多因素影响,晶振的一些重要参数会因工作温度、激励功率、负性阻抗等变化而变化。因此,我们对晶振的重要参数了解的越多,越有益于晶振采购及选型。另外,不会再一味的追求更低的晶振价格,而忽视了晶振本身的品质及性能的重要性,毕竟产品的品质才是良好口碑的有力保…

哪些晶振参数对振荡电路有较大影响?

2020-11-10基于晶振内部核心部件石英水晶片材质特性及生产工艺等诸多因素影响,晶振的一些重要参数会因工作温度、激励功率、负性阻抗等变化而变化。因此,我们对晶振的重要参数了解的越多,越有益于晶振采购及选型。另外,不会再一味的追求更低的晶振价格,而忽视了晶振本身的品质及性能的重要性,毕竟产品的品质才是良好口碑的有力保… -

; ) 晶振激励功率和负性阻抗实测及计算方法

2020-11-10尽管在晶振振荡电路设计之前,我们都会从IC方案中获取晶振相关信息,如晶振封装、频率、频差、负载电容、工作电压等,但在晶振实际电路应用中,我们却会遇到一些具体问题,比如按照BOM采购晶振,在电路板上电后,发生晶振不良导致电路板显示不上电或某些功能失效等问题。在不少方案设计中,晶振的作用是…

晶振激励功率和负性阻抗实测及计算方法

2020-11-10尽管在晶振振荡电路设计之前,我们都会从IC方案中获取晶振相关信息,如晶振封装、频率、频差、负载电容、工作电压等,但在晶振实际电路应用中,我们却会遇到一些具体问题,比如按照BOM采购晶振,在电路板上电后,发生晶振不良导致电路板显示不上电或某些功能失效等问题。在不少方案设计中,晶振的作用是… -

; ) 晶振应用中的两个重要参数:激励功率与负性阻抗

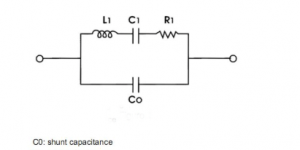

2020-11-09首先确定一点,晶振激励功率与负性阻抗这两个概念仅是针对无源晶振而言。在晶振的实际电路应用中,排除晶振品质不良之外,就只剩电路应用不当导致的晶振不起振问题了。显然,晶振的激励功率与晶振电路负性阻抗是我们不可规避的两个重要概念,也是我们必须要搞清楚的两个晶振电路专业术语。 晶振激励功率(英文名称:D…

晶振应用中的两个重要参数:激励功率与负性阻抗

2020-11-09首先确定一点,晶振激励功率与负性阻抗这两个概念仅是针对无源晶振而言。在晶振的实际电路应用中,排除晶振品质不良之外,就只剩电路应用不当导致的晶振不起振问题了。显然,晶振的激励功率与晶振电路负性阻抗是我们不可规避的两个重要概念,也是我们必须要搞清楚的两个晶振电路专业术语。 晶振激励功率(英文名称:D… -

; ) 如何避免有源晶振被烧坏导致失效?

2020-11-09在有源晶振电路应用中,有源晶振(OSC、晶体振荡器)需要特别注意以下两点: 有源晶振具有方向性,因此万万不可贴反,否则存在失效高风险。 电源输入时,严格遵循规格书电压额定范围(±10%),否则若电压过高,同样容易造成电流烧坏有源晶振导致晶振失效。 有源晶振(英文oscillator),全称为石英晶体…

如何避免有源晶振被烧坏导致失效?

2020-11-09在有源晶振电路应用中,有源晶振(OSC、晶体振荡器)需要特别注意以下两点: 有源晶振具有方向性,因此万万不可贴反,否则存在失效高风险。 电源输入时,严格遵循规格书电压额定范围(±10%),否则若电压过高,同样容易造成电流烧坏有源晶振导致晶振失效。 有源晶振(英文oscillator),全称为石英晶体… -

; ) 晶振不起振:造成晶振DLD2不良的原因有哪些?

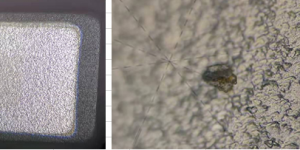

2020-11-08(受污染的石英晶片放大图:异物/杂质导致晶振失效) 晶振在实际电路中,最常见的不良现象为:晶振不起振、频偏及不稳定。排除电路应用因素之外,显然,晶振本身性能不良也占有不少比重。晶振DLD2不良是相对最严重的一种不良现象,将直接导致晶振不起振及/或时振时不振,有效应对措施只有通过重工来更换晶振。 导致…

晶振不起振:造成晶振DLD2不良的原因有哪些?

2020-11-08(受污染的石英晶片放大图:异物/杂质导致晶振失效) 晶振在实际电路中,最常见的不良现象为:晶振不起振、频偏及不稳定。排除电路应用因素之外,显然,晶振本身性能不良也占有不少比重。晶振DLD2不良是相对最严重的一种不良现象,将直接导致晶振不起振及/或时振时不振,有效应对措施只有通过重工来更换晶振。 导致… -

; ) 晶振PCB布线设计:晶振两端布线需要长度一样吗?

2020-11-08首先需要指出的是,只有无源晶振除了频率输出脚,还有另外一个频率输入脚。有源晶振没有频率输入脚,它的主要脚位包括电压输入脚与频率输出脚,因此这里所指的“晶振两端布线长度”为无源晶振,即石英晶体谐振器(Crystal),而非有源晶振(OSC)。 无源晶振两端(即频率输出脚与输入脚)布线长度尽量等同,并且…

晶振PCB布线设计:晶振两端布线需要长度一样吗?

2020-11-08首先需要指出的是,只有无源晶振除了频率输出脚,还有另外一个频率输入脚。有源晶振没有频率输入脚,它的主要脚位包括电压输入脚与频率输出脚,因此这里所指的“晶振两端布线长度”为无源晶振,即石英晶体谐振器(Crystal),而非有源晶振(OSC)。 无源晶振两端(即频率输出脚与输入脚)布线长度尽量等同,并且… -

; ) 时钟时间不准与晶振32.768KHz的精度有什么关系?

2020-11-07如果你的手表是电子石英表,你知道里面必有一颗石英晶振32.768KHz吗?它在不停的以每秒32768次的频率在振动,为你提供时间服务。 石英晶振32.768KHz工作原理 石英是一种具有压电特性的物质,如果在两面加力就会出现电荷,同时压电材料也有反向作用。所以当给石英晶片通电后,晶片就会持续产生频率…

时钟时间不准与晶振32.768KHz的精度有什么关系?

2020-11-07如果你的手表是电子石英表,你知道里面必有一颗石英晶振32.768KHz吗?它在不停的以每秒32768次的频率在振动,为你提供时间服务。 石英晶振32.768KHz工作原理 石英是一种具有压电特性的物质,如果在两面加力就会出现电荷,同时压电材料也有反向作用。所以当给石英晶片通电后,晶片就会持续产生频率…